#### Exploiting Body Terminals of Transistors for Performing Post-Fabrication Tests, Run-Time Tests, and Self-Adaptive Bias in Integrated Circuits

Rodrigo Possamai Bastos

#### ▶ To cite this version:

Rodrigo Possamai Bastos. Exploiting Body Terminals of Transistors for Performing Post-Fabrication Tests, Run-Time Tests, and Self-Adaptive Bias in Integrated Circuits. Micro and nanotechnologies/Microelectronics. Univ. Grenoble Alpes, January 30, 2018. tel-02989324

#### HAL Id: tel-02989324 https://hal.univ-grenoble-alpes.fr/tel-02989324v1

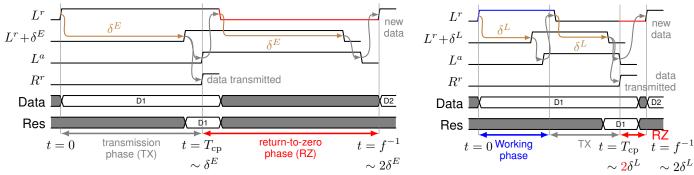

Submitted on 5 Nov 2020

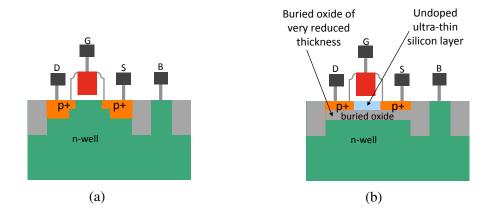

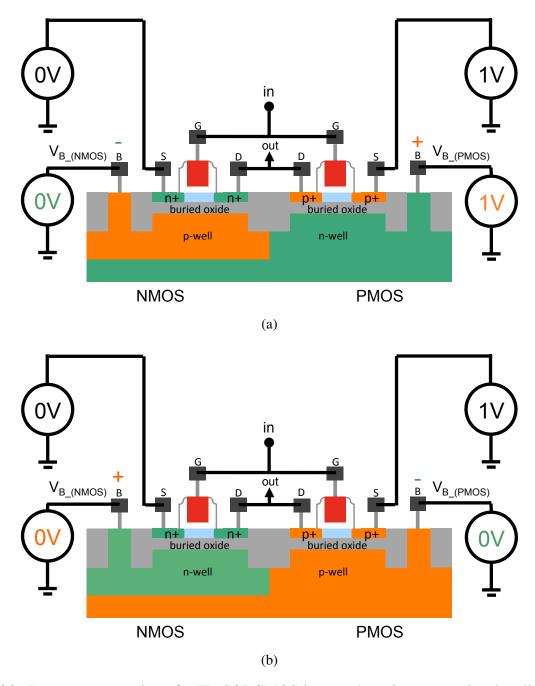

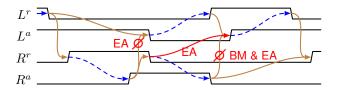

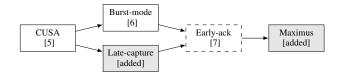

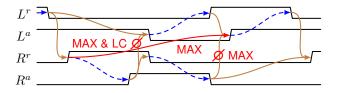

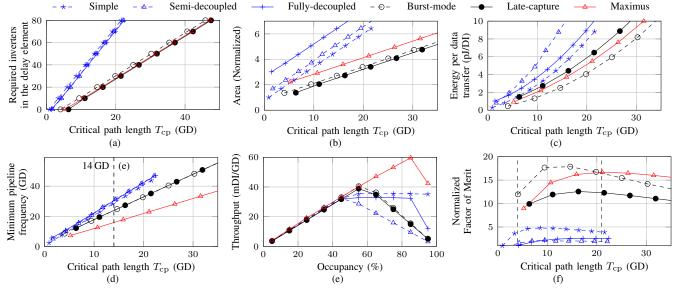

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE**

Pour obtenir l'Habilitation à Diriger des Recherches (HDR) de la

#### COMMUNAUTÉ UNIVERSITÉ GRENOBLE ALPES

Spécialité : Nano Électronique & Nano Technologies

Présentée par

#### Rodrigo POSSAMAI BASTOS

Préparée au sein du Laboratoire TIMA dans l'École Doctorale Electronique, Electrotechnique, Automatique & Traitement du Signal (E.E.A.T.S)

# Exploiting Body Terminals of Transistors for Performing Post-Fabrication Tests, Run-Time Tests, and Self-Adaptive Bias in Integrated Circuits

Thèse soutenue publiquement le 30/01/2018, devant le jury composé de :

#### M. Pascal FOUILLAT

Full Professor, Bordeaux INP, IMS (France), Président

Mme. Edith BEIGNE

Senior Scientist, CEA Leti (France), Rapporteur

#### M. Bernabé LINARES-BARRANCO

Full Professor, IMSE-CNM (Spain), Rapporteur

#### M. Matteo SONZA REORDA

Full Professor, Politecnico di Torino (Italy), Rapporteur

#### M. Patrick GIRARD

CNRS Research Director, LIRMM (France), Examinateur

#### M. Raoul VELAZCO

CNRS Research Director, TIMA (France), Examinateur

#### M. Haralampos STRATIGOPOULOS

CNRS Researcher, UPMC, LIP6 (France), Examinateur

#### **Table of contents**

| A١ | bstrac | et e e e e e e e e e e e e e e e e e e                                        | V  |  |  |

|----|--------|-------------------------------------------------------------------------------|----|--|--|

| Ι  | Res    | search activities                                                             | 1  |  |  |

| 1  | Intr   | oduction                                                                      | 3  |  |  |

| 2  | Effe   | ctiveness of error detection techniques in identifying transient faults       | 5  |  |  |

|    | 2.1    | Techniques for Concurrent Error Detection (CED)                               | 6  |  |  |

|    | 2.2    | Proposed CED technique                                                        | 7  |  |  |

|    | 2.3    | Method for evaluation of CED techniques                                       | 10 |  |  |

|    | 2.4    | Simulation results and comparative analysis                                   | 13 |  |  |

|    | 2.5    | Conclusions                                                                   | 15 |  |  |

| 3  | Arc    | hitectures of body built-in current sensors for detection of transient faults | 17 |  |  |

|    | 3.1    | State-of-the-art architectures of built-in current sensors                    | 17 |  |  |

|    | 3.2    | New dynamic BBICS architecture                                                | 24 |  |  |

|    | 3.3    | Sensitivity of a flip-flop in detecting transient faults                      | 27 |  |  |

|    | 3.4    | Analysis and comparison of BBICS sensitivities in detecting transient faults  | 28 |  |  |

|    | 3.5    | Conclusions                                                                   | 36 |  |  |

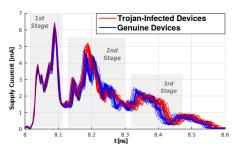

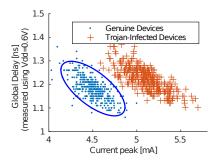

| 4  | Mor    | nitoring body terminals of transistors for detection of layout-level Trojans  | 37 |  |  |

|    | 4.1    | Background                                                                    | 38 |  |  |

|    | 4.2    | Proposed HT detection method                                                  | 41 |  |  |

|    | 4.3    | Simulation results and analysis                                               | 44 |  |  |

|    | 4.4    | Conclusions                                                                   | 46 |  |  |

| 5  | Leve   | el shifter for dynamically biasing ultra-low voltage subcircuits of systems   | 47 |  |  |

|    | 5.1    | State-of-the-art level shifter architectures                                  | 48 |  |  |

|    | 5.2    | Proposed level shifter architecture                                           | 50 |  |  |

|    | 5.3    | Simulation results and analysis                                               | 51 |  |  |

|    | 5.4    | Conclusions                                                                   | 53 |  |  |

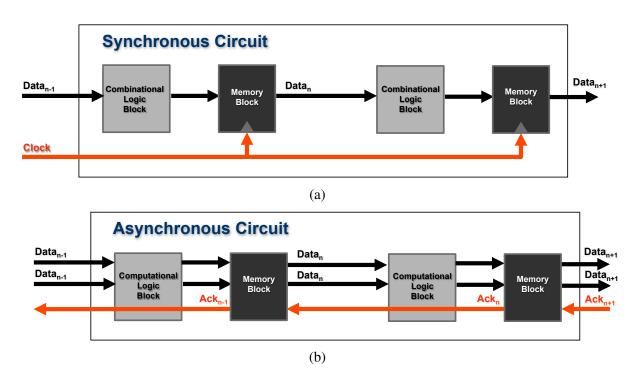

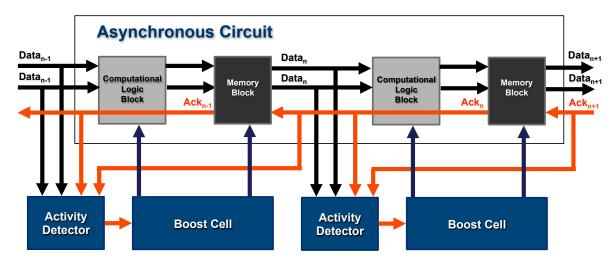

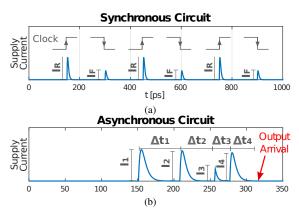

| 6  | Ultr   | Ultra-low voltage asynchronous circuits in FD-SOI technology                  |    |  |  |

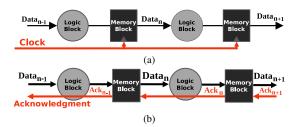

|    | 6.1    | Asynchronous circuits and FD-SOI technology                                   | 56 |  |  |

|    | 6.2    | Exploiting intrinsic features of QDI asynchronous circuits for saving power   | 59 |  |  |

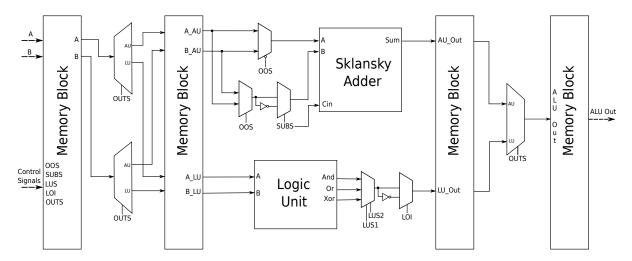

|    | 6.3    | Case-study circuits: synchronous and asynchronous ALU                         | 60 |  |  |

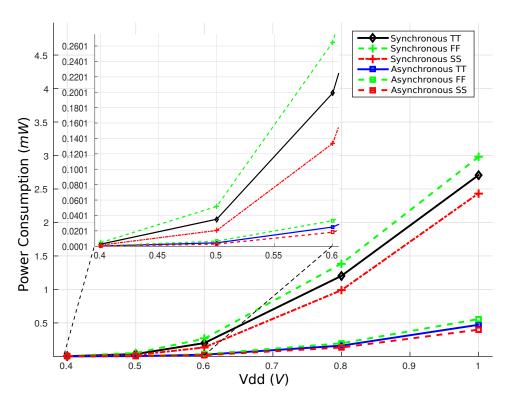

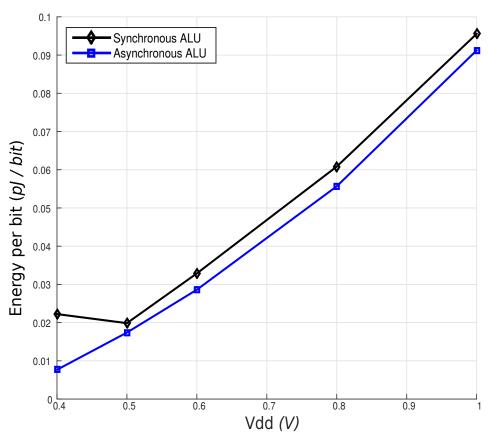

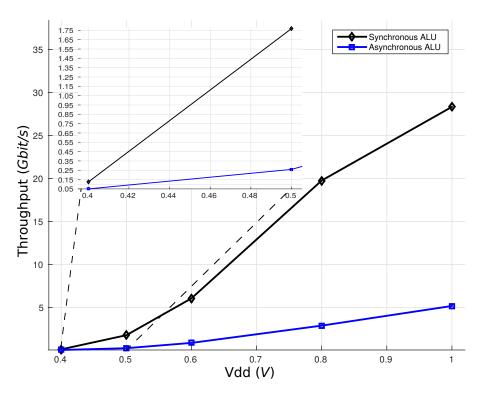

|    | 6.4    | Synchronous and asynchronous ALU results                                      | 61 |  |  |

|    |        |                                                                               |    |  |  |

|    | 6.5        | Conclusions                                                                                                                      | 64       |

|----|------------|----------------------------------------------------------------------------------------------------------------------------------|----------|

| 7  | Con        | clusions and perspectives                                                                                                        | 65       |

|    | 7.1        | Short-term perspectives                                                                                                          | 66       |

|    | 7.2        | Medium-term perspectives                                                                                                         |          |

|    | 7.3        | Long-term perspectives                                                                                                           | 68       |

| Re | eferen     | ces                                                                                                                              | 69       |

| II | Cı         | ırriculum vitae                                                                                                                  | 81       |

| 1  | Iden       | tification et parcours professionnel                                                                                             | 83       |

| 2  | Pub        | lications et production scientifique                                                                                             | 85       |

|    | 2.1        | Travaux soutenus devant un jury                                                                                                  | 85       |

|    | 2.2        | Articles dans des revues d'audience internationale                                                                               | 85       |

|    | 2.3        | Conférences internationales avec comité de lecture et actes                                                                      |          |

|    | 2.4        | Conférences internationales avec comité de lecture                                                                               |          |

|    | 2.5        | Colloques nationaux                                                                                                              |          |

|    | 2.6        | Colloques régionaux                                                                                                              | 91       |

| 3  | Enca       | adrements scientifiques                                                                                                          | 93       |

|    | 3.1        | Thèses de doctorat (soutenances en début décembre 2017)                                                                          |          |

|    | 3.2        | Thèses de doctorat en cours                                                                                                      |          |

|    | 3.3        | Stages de fin d'études en niveau master 2 ou 3ème année d'écoles d'ingénieurs                                                    | 95       |

| 4  |            | usion des travaux (rayonnement et vulgarisation)                                                                                 | 97       |

|    | 4.1        | Distinctions                                                                                                                     |          |

|    | 4.2        | Membre de jury en soutenances de doctorat, master et travail de fin d'études                                                     |          |

|    | 4.3        | Implication en comités de conférences                                                                                            |          |

|    | 4.4        | Rapporteur d'articles de revues et conférences                                                                                   | 99<br>99 |

|    | 4.5<br>4.6 | Institutions et entreprises ayant des projets en coopérations directement établies<br>Communications sur invitation (séminaires) |          |

| 5  | Rest       | oonsabilités scientifiques et pédagogiques                                                                                       | 101      |

|    | 5.1        | Responsable de projets scientifiques                                                                                             |          |

|    | 5.2        | Co-responsable de projets scientifiques                                                                                          |          |

|    | 5.3        | Membre de conseil de laboratoire                                                                                                 |          |

|    | 5.4        | Responsable d'activités pédagogiques                                                                                             |          |

| 6  | Résu       | ımé d'activités de recherche                                                                                                     | 105      |

|    | 6.1        | Introduction                                                                                                                     |          |

|    | 6.2        | Main research activities and scientific contributions                                                                            | 105      |

| II | I A        | ppendix: some complementary works                                                                                                | 107      |

|    |            | cle in international IFFF conference: DATF 2018                                                                                  | 100      |

| В | Article in international ACM conference: ISPD 2018                           | 114 |

|---|------------------------------------------------------------------------------|-----|

| C | Article in international journal: Elsevier Microelectronics Reliability 2017 | 123 |

| D | Article awarded in international IEEE/ACM conference: SBCCI 2016             | 132 |

| E | Article in international journal: Springer JETTA 2013                        | 139 |

#### **Abstract**

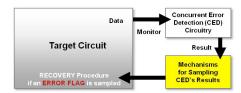

Ubiquitous integrated circuit applications help the humanity to rapidly evolve by supporting electronics systems that are more and more assuming autonomous functions and decisions of important responsibility for the society. In this context, dealing with security, reliability, and power issues of integrated circuits is fundamental to ensure the operation of systems within reasonable levels of privacy, safety, and energy consumption. Exploiting body terminals of transistors in CMOS technology-based systems, this work contributes with new techniques dedicated to: (a) test circuits – just after fabrication – for detecting possible hardware Trojans inserted to maliciously compromise systems; (b) test circuits on the fly for detecting transient faults provoked by radiation effects or malicious attacks; and (c) perform body bias adaptation in systems aiming to optimize speed and power but also compensate threshold voltage alterations induced by aging, process, voltage, and temperature variations. Moreover, herein, ongoing and near-future related activities and insights are discussed as potential perspectives of this work.

# Part I Research activities

#### Chapter 1

#### Introduction

Many types of new-generation electronics systems surround nowadays our lives, providing solutions, utilities, and conveniences we had never experimented before. Biomedical, agricultural, industrial, commercial, service, entertainment, home, automobile, aeronautical, space, and telecommunication appliances help us to solve quotidian problems related, for instance, to the health of living beings, transport over short and long distances, satellite TV broadcast, weather forecast, and communication between computers and people. From a new world of the Internet of things (IoT) in which billions of communicating devices harvest data from tens of billions of sensors, dealing with security, reliability, and power issues becomes more and more important for integrated circuit (IC) applications.

The information technology (IT) sector – as the heart of the IoT with its data centers, communication networks, and end-user devices – was already responsible in 2012 for around 7 % of the world's electricity demand [25], including the energy required to manufacture IT infrastructures and equipments. It is approximately fourfold higher than the total energy consumption of a Brazil-like country in the same year. The need for reducing power is, therefore, immediate, not only to have our mobile telephones and battery-powered portable gadgets working for a longer time without recharging, but also to make our planet greener again by saving natural resources.

Parallelly, in the advent of self-adaptive systems like geolocation satellites, aircraft, drones, autonomous cars, nuclear power plant robots, in-body-implanted medical devices – which are all applications of high risk in case of failure – embedded circuits must be sufficiently reliable, safely operating within a specified range of low-power performance even in harsh environments. Furthermore, circuits embedded in such critical applications must also be conveniently secure, hiding confidential data, restricting access to private information, and defending themselves from intentional attacks that aim to hack into systems for maliciously carrying out illegal actions or inducing catastrophic situations.

This work is specifically interested to deal with three important issues related to the security, reliability, and power of integrated systems in complementary metal—oxide—semiconductor (CMOS) technologies: (a) hardware Trojans (HT), which are malicious slight layout alterations or furtive mechanisms [126] included in outsourced IC design, fabrication, or manufacturing phases by third-party suppliers willing to hack, disturb, or intentionally disable, at run time, the Trojan-infected circuits; (b) transient faults (TF), as voltage glitches induced by radiation [55] or malicious sources [5, 15, 39, 56] of perturbation, can provoke bit flips in memory elements — i.e. soft errors that may lead entire systems to fail, compromising critical applications or even providing relevant information for cryptanalysis methods that exploit results of fault-injection attacks over secure circuits; and (c) transistor threshold voltage (Vth) alterations — induced by

aging, process, voltage, and temperature (PVT) variations as well as by body bias modifications – are able not only to slow down gates of circuits, violating critical timing constraints, but also speed up them at the expense of static power consumption increase [37, 128].

Efficiently making integrated systems low-power, reliable, and secure to HT, TF, and Vth alterations requires the inclusion of dedicated hardware-level techniques, incurring extra costs in terms of area, power, or speed. For detecting HT, post-fabrication testing schemes [1,2,13,16, 52,86,92,97,134,144] have to be implemented for seeking malicious hardware modifications in the IC under test. For detecting TF, otherwise, run-time testing mechanisms [3,12,29,82,91, 93,94,100,113,121] need to be embedded in the systems for dynamically monitoring illegal voltage glitches. And for compensating Vth alterations, adaptive body bias generators [10, 37, 44, 53, 77, 128] are added to intelligently tune Vth of transistors in function of aging and PVT variations.

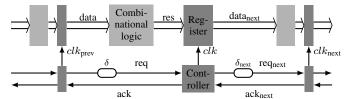

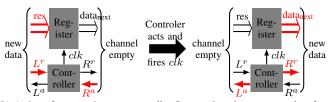

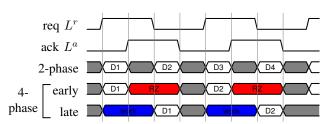

Exploiting the body terminals of transistors, this work contributes with new techniques of: (a) post-fabrication test for detecting HT; (b) run-time test for detecting TF; and (c) body bias for systems targeting adaptive compensation of Vth alterations but also optimization of speed and power. Chapter 2 of this work evaluates the effectiveness of state-of-the-art TF-detection techniques, moreover it proposes a new concurrent error detection scheme. Chapter 3 analyzes different architectures of bulk built-in current sensors (BBICS) able to monitor body terminals of transistors for detecting single or multiple TF. A new low-cost and efficient dynamic BBICS architecture is also presented in chapter 3. Chapter 4, on the other hand, presents a novel postfabrication testing method for the detection of HT by using BBICS, which also operate to detect TF at run time. Chapter 5 studies a mechanism that is fundamental for applying adaptive body bias strategies: the voltage level shifter. In addition, it introduces a new level shifter architecture for dynamically biasing low-voltage subcircuits of fine-grained systems. Finally, chapter 6 analyzes the suitability of asynchronous circuits, which deal with data without using a clock, for receiving adaptive body bias schemes, properly operating with low voltages, and controlling themselves their static power consumption and speed. Chapter 7 concludes this work discussing the most important contributions and results, and ongoing and near-future perspectives.

#### Chapter 2

## Effectiveness of error detection techniques in identifying transient faults

With the downscale of integrated systems, increasing their robustness against environment- or human-induced perturbations motivates considerable design challenges. Aging effects, alpha particles released by radioactive impurities, and more importantly, neutrons from cosmic rays are examples of environmental events [55]. In addition, fault injections to the end of retrieving secret data from security applications or disabling embedded secure protocols are human-produced attacks, which try to obtain fundamental information for cryptanalysis methods [56] or to activate hardware Trojans maliciously inserted in systems [126].

Radiation exposure and environmental variations are able to induce parasitic transient currents that may lead integrated circuits to critical failures. Similar electrical effects are also caused by optical sources like flashlights or laser beams [39], which allow, moreover, finely controlling the injected current thanks to the high spatial and temporal resolutions of laser shots [5]. The induced transient faults (TFs) – i.e. temporarily voltage level modifications – are active only for a short duration of time, their occurrence are not predictable, and they may provoke soft errors (SEs) in stored results of system operations. TFs need thus to be detected at run time.

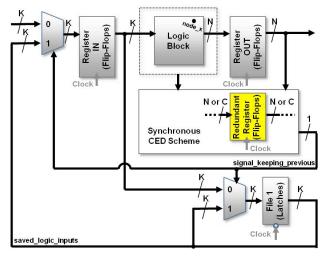

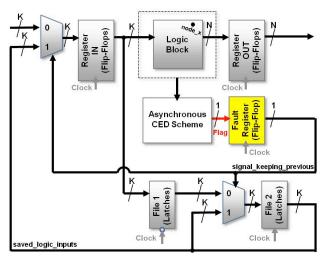

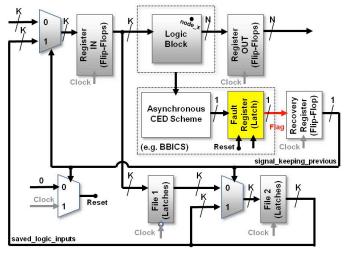

Error detection during circuit normal operation is typically called concurrent error detection (CED) [81]. Several CED techniques have been proposed [3,12,29,34,91,93,100,113,115,121] with the intent to design more reliable computing systems. These techniques mainly differ in their detection capabilities and in the constraints they impose on the system design. This chapter presents a simulation-based method to evaluate and compare different detection techniques regarding their effectivenesses in detecting TFs arisen in combinational logic blocks and resulting in SEs. The method proposes 32 different scenarios of TF injection. Results of all detection techniques studied here are summarized in a table that provides a direct insight of the effectiveness of each technique. Furthermore, in this chapter, another CED technique is introduced and compared among the other techniques. It uses an effective Transition Detector (TD) and a controllable adaptive detection window (DW). As a result, the introduced technique offers increased SE detection capability but also allows the detection of Delay Errors (DEs). The works of this chapter are the prospects of my postdoctoral activities started at 2010, and within the thesis context of my Ph.D. student Raphael Viera, it was presented in the international conference ESREF 2017 and published in the international journal Microelectronics Reliability 2017.

Section 2.1 of this chapter describes the main CED techniques in the literature and section 2.2 details our improved CED technique. In the following, section 2.3, 2.4, and 2.5 present our method for evaluating the effectiveness of CED techniques, simulation results, and comparative analysis.

#### 2.1 Techniques for Concurrent Error Detection (CED)

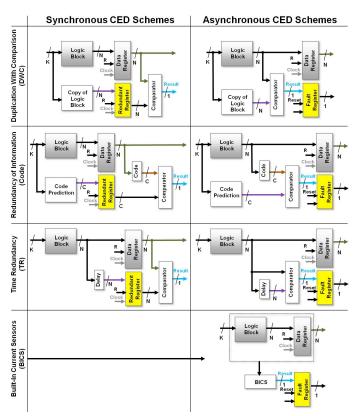

State-of-the-art CED techniques are classified in this section into four categories: spatial redundancy, temporal redundancy, Transition Detector (TD)-based schemes, and Built-In Current Sensors (BICSs). We could still mention a fifth category – information redundancy – in which its structure is similar to a spatial redundancy; however, instead of a copy block, a code prediction block and a coder are added [109]. Furthermore, we highlight the well-known acronym CED is indeed a misuse of language as there exist concurrent detection schemes able to detect transient faults (TFs) not necessarily producing errors. The detection of TFs that are masked – not resulting in hard or soft errors (SEs) – is also of importance for secure applications. All these approaches are implementable at different abstraction levels of a design, this work is interested in techniques at hardware level.

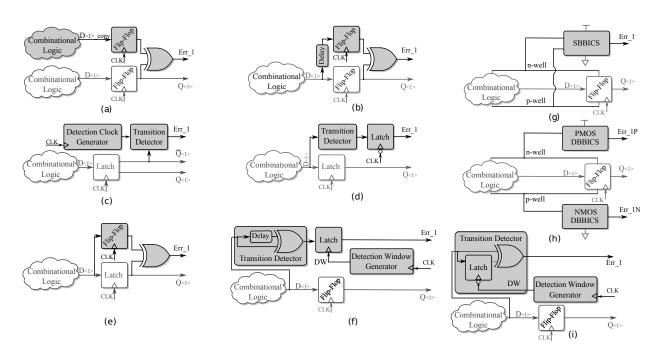

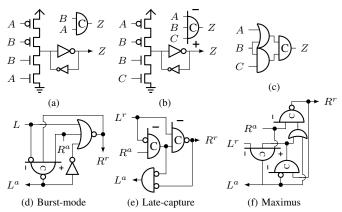

#### 2.1.1 Spatial redundancy

• **Duplication With Comparison (DWC)** technique [115] – illustrated in Fig. 2.1a – is conceptually the simplest CED scheme. Based on the principle of spatial redundancy, the outputs  $D_{<1>}$  and  $D_{<1>}$  copy (duplication of the circuit's logic) are connected to two D-type Flip-Flops (DFFs), which have their outputs compared, generating an error signal in case of difference.

#### 2.1.2 Temporal redundancy

• Time Redundancy (TR) technique [93] (Fig. 2.1b) repeats the same computation with the same hardware at different time instants. The output of the two DFFs are compared, and if the outputs are divergent, the error signal is raised.

#### 2.1.3 Transition Detector (TD)-based schemes

- RAZOR-II [29] is a TD-based technique dedicated to detect Delay Errors (DEs) but also the advent of SEs. A simplified circuit diagram of this scheme is shown in Fig. 2.1c. The design assumption is that the latch output  $Q_{<1>}$  is allowed to shortly switch only after a rising edge of the clock CLK. The latch output  $\overline{Q}_{<1>}$  is connected to a TD block that is thus able to detect TFs. To avoid false error signaling, a detection clock generator disables the TD block for at least the duration of the CLK-to $Q_{<1>}$  delay after a rising edge of CLK.

- Transition Detector With Time Borrowing (TDTB) technique [12] is similar to Razor-II. It consists in the coupling of a latch and a TD as illustrated in Fig. 2.1d. The transition detector raises the error signal for any input transitions during the low state of the clock  $(\overline{CLK})$ , thus requiring the signal  $D_{<1>}$  to be stable before the low period of the clock.

- Double Sampling With Time-Borrowing (DSTB) technique [12] presented in Fig. 2.1e is like TDTB scheme although a shadow flip-flop replaces the TD block. DSTB double samples signal  $D_{<1>}$  and compares the latch and shadow flip-flop outputs to generate the error signal. Furthermore, DSTB retains the time-borrowing feature of TDTB to eliminate data-path metastability.

• Transient Fault Monitoring Scheme (TFMS) proposed in [113] detects TFs affecting the DFF input such as signal  $D_{<1>}$ . As shown in Fig. 2.1f, this scheme includes a *Transition Detector*, which generates a high signal when there is a TF inside the *Detection Window* (signal "DW"). The *Sticky Block* is used to validate TFs occurring only inside the DW and to merge the error signal since the TD produces two pulses.

#### 2.1.4 Built-In Current Sensors (BICSs)

- Single Bulk Built-In Current Sensor (SBBICS) [108] [34] is an optimized version of the original bulk BBICS [91] designed to monitor radiation- or laser-induced transient currents passing through the bulk of transistors. The SBBICS architecture allows monitoring simultaneously the pull-up and pull-down of CMOS networks [108] [34] as shown in Fig. 2.1g. Chapter 3 further details how BICS architectures detect TFs.

- Dynamic Bulk Built-In Current Sensor (DBBICS) [121] operates similarly to SBBICS, although it features a dynamic memory cell. The TF occurrence information is stored in the gate-source capacitance of a storage transistor. Two DBBICS architectures are abstracted in Fig. 2.1h to individually monitor the pull-up and pull-down CMOS networks.

Fig. 2.1: CED techniques: (a) DWC [115]; (b) TR [93]; (c) Razor-II [29]; (d) TDTB [12]; (e) DSTB [12]; (f) TFMS [113]; (g) SBBICS [34]; (h) DBBICS [121]; and (i) the CED technique proposed in section 2.2: Latch Based Transient-Fault Detection (LBTFD).

#### 2.2 Proposed CED technique

The technique presented in this section is proposed to improve the effectiveness of TD-based schemes in detecting transient faults. The operation mode is similar to schemes [113] and [100]. However the devised 1-bit TD circuit is formed by a latch instead of the delay block suggested

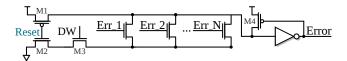

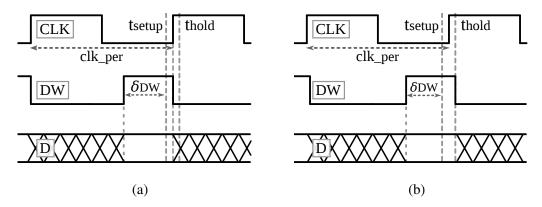

in [113] and [100], as shown in Fig. 2.1i. In addition, unlike previous works [113] and [100], our proposition combines the error signals of each 1-bit TD circuit ( $Err\_1$  to  $Err\_N$ ) with the help of a single dynamic OR gate (Fig. 2.2), and not using parity trees (i.e. xor trees) that may electrically filters TF and prevent the possibility of detecting them. The proposed TD circuit and dynamic OR gate are particularly activated during a Detection Window (DW) in which the monitored combinational circuit's output  $D_{<1>}$  (i.e. D-type Flip-Flop (DFF) input) is prone to present TF-induced illegal transitions. Therefore, any abnormal transition at  $D_{<1>}$  within DW would be detected. We denote our technique herein as Latch Based Transient-Fault Detection (LBTFD). The scheme in Fig. 2.3 is used to specify the signal called DW.

One of the advantages in using a latch as a TD is that only one pulse is generated by the error signal output. In the case of a TD, as the one used in [113], the transition detection block produces two pulses, therefore, needing to recur to an additional block to merge the two generated pulses. A second advantage is the ability to detect TFs during the hold time (thus TFs inducing SE). An additional increase in  $\delta 2$  will enable the detection to further cover SEs and DEs. Furthermore, the use of a latch in a TD will guarantee the detection of TFs in recent technologies as TDs using inverters connected to a XOR gate [12] need an increased delay in order to be triggered, thus, having more static power consumption and higher area overhead.

Fig. 2.2: Dynamic OR gate for combining error signals from TD circuits.

Fig. 2.3: Generator of the Detection Window (DW) signal.

#### 2.2.1 Defining the Detection Window (DW)

In order to choose a proper configuration for DW, Fig. 2.4a refers to a data-path with a clock period denominated  $clk\_per$ . Labels  $t_{setup}$  and  $t_{hold}$  define the DFF setup and hold times respectively. The setup time is the minimum amount of time before the clock edge during which the signal  $D_{<1>}$  must be valid, whereas the hold time is the minimum amount of time after the clock edge during which the signal  $D_{<1>}$  must be valid for a correct operation of the DFF.  $\delta_{DW}$  is the time overhead due to the DW. According to the width of TFs  $(TF_W)$ , the width of the DW  $(DW_{width})$  can be designed in a way in which only faults resulting in SEs are detected:

$$DW_{width} = (t_{setup} + t_{hold}) (2.1)$$

or, in which TFs resulting or not resulting in SEs are detected:

$$DW_{width} = (t_{setup} + t_{hold}) + \delta_{DW}. \tag{2.2}$$

Note that, the greater the  $\delta_{DW}$  (lower  $\delta 1$  in Fig. 2.3), the earlier the signal  $D_{<1>}$  must be steady. Indeed it must reach its final steady state before  $(t_{setup} + \delta_{DW})$ . For a DW configuration as the one in Fig. 2.4a the maximum operating clock frequency of the circuit is penalized,

however,  $\delta 2$  allows a shift in DW meanwhile maintaining its same width as can be seen in Fig. 2.4b, thus allowing an increased operation frequency of the circuit. In fact there are many ways to design DW to coper with timing specifications. The main advantage in having  $\delta_{DW} \neq \emptyset$  is the possibility to assure the detection of transient faults with  $TF_W \leq (t_{setup} + t_{hold} + \delta_{DW})$  that will cause a SE.

Fig. 2.4: Detection Window (DW) configuration: (a)  $\delta 1 \neq 0$  and  $\delta 2 = 0$  (b)  $\delta 1 \neq 0$  and  $\delta 2 \neq 0$ .

#### 2.2.2 Verification by electrical simulation

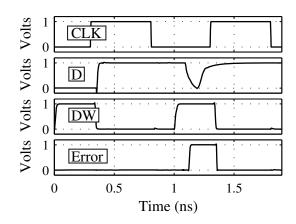

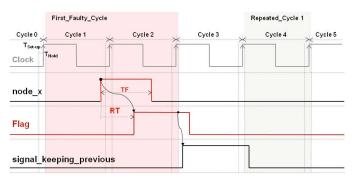

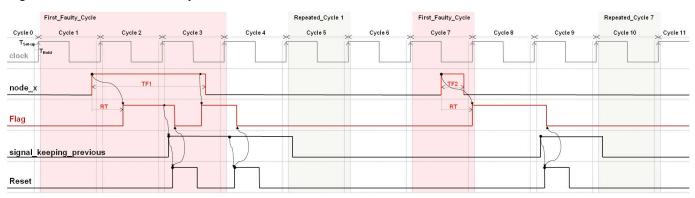

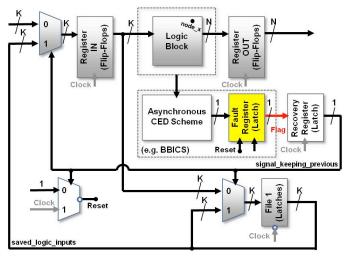

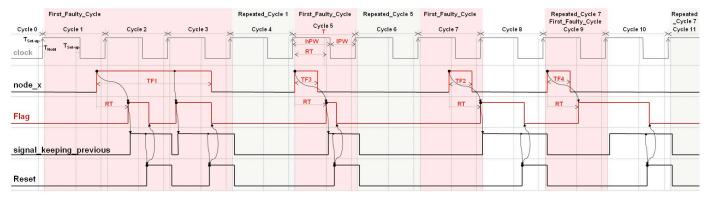

The operation mode of the proposed technique has been verified by electrical simulation to detect the advent of a single induced transient fault arriving at node  $D_{<1>}$  as presented in Fig. 2.5. The simulation has been performed in the FD-SOI 28 nm technology with VDD = 1 V. The injected transient current magnitude was a value from which the associated transient voltage amplitude (created at node  $D_{<1>}$ ) is equivalent to 100% of VDD, i.e. 1 V. The transient fault width was set to be around 150 ps, with rise time (tr) shorter than the fall time (tf) to keep the traditional shape of transient faults [137] [80] [17] [32] [36]. The transient current has been injected from a NMOS sensitive drain  $D_{<1>}$  to its p-well bulk, i.e. the current has been applied when  $D_{<1>}$  was steady at 1 V. It could be clearly noted that any variation inside the DW is sufficient to trigger the error signal independently of its polarity (rising or falling). Therefore, any fault occurring in the NMOS or PMOS sensitive drains within the DW is detectable.

Fig. 2.5: Electrical simulation of the proposed technique detecting a single TF (width of around 150 ps) injected on node  $D_{<1>}$ .

#### 2.3 Method for evaluation of CED techniques

The method proposed in this section evaluates the effectiveness of CED techniques in detecting single TFs by taking advantage of four facts:

- (1) The harmful consequence of TFs induced in a target combinational circuit under protection of a CED circuitry is the generation of a SE in one or several DFFs;

- (2) TFs induced inside of a target combinational circuit at the worst case propagate up to an input  $D_{<1>}^{1}$  of one or several DFFs flipping their bits (SEs);

- (3) TFs partially or fully propagated up to  $D_{<1>}$  produce a profile of TF on  $D_{<1>}$  that is perfectly representable by profiles of single TFs injected directly on  $D_{<1>}$ ; and

- (4) TFs induced inside of a target combinational circuit and fully mitigated by a logical or electrical masking effect [55] make no effect on  $D_{<1>}$ . These TFs are indeed attenuated by the target combinational circuit, and not by the CED technique protecting it.

With these four TF-related facts in mind, the evaluation of the CED technique effectiveness can be simplified by injecting TFs only on  $D_{<1>}$ . Furthermore, as the goal is evaluating the degree to which a CED technique is successful in detecting TFs – and not the ability of the target combinational circuit in logically or electrically masking TFs – the logic function of the target combinational circuit is not relevant. Latching-window masking effects, otherwise, have to be considered because the sampling window of DFFs is directly related to the design of most CED techniques included into systems synchronized by a clock.

The proposed simulation-based method applies, therefore, only on  $D_{<1>}$  a double exponential current source with parameters configurable according to the classical single TF model for CMOS circuits [137] [80]. Diversified profiles of single TFs are thus injected on  $D_{<1>}$  at different instants, and the results of the TF-injection campaigns are synthesized through evaluation metrics.

#### 2.3.1 Profiles of injected TFs

Campaigns of single current injections reproduce 32 scenarios having different profiles of TFs: transient faults with different widths, current amplitudes, and polarities (sensitive drain). The rise times of the injected double exponential current sources have been set on the order of 5 ps to keep the typical shapes of TFs: short rise time and longer fall time [32] [36]. Additionally, the slack time left by the target combinational circuit is changed to verify how a CED technique behaves when data on  $D_{<1>}$  stabilizes during high and low levels of the clock. By scenario, a total of one thousand TFs, for instance, are injected across a clock period of 1 ns, resulting in a simulation step of 1 ps.

The 32 scenarios are summarized in Table 2.1. By considering a simulation start time of 0 ns, the TF start column represents the instant at which the first transient fault begins to be injected on node  $D_{<1>}$ . Note that the combination of each column in the table comprises a different scenario, resulting in a total of 32 scenarios, for instance, the eight scenarios in the first row (1, 2, 9, 10, 17, 18, 25 and 26) have the following possible configurations: TF width of 10 ps, TF start at 0.2 ns or 0.58 ns, sensitive drain of PMOS or NMOS and TF amplitude of 60%VDD or 100%VDD.

$<sup>{}^{1}</sup>D_{<1>}$  represents 1 bit of N bits, e.g., a system of 32 bits would require the inclusion of 32 CED circuitries.

Table 2.1: Profiles of injected TFs

|               | TF    | TF    |           | TF        |

|---------------|-------|-------|-----------|-----------|

| Scenario      | width | start | Sensitive | amplitude |

|               | (ps)  | (ns)  | Drain     | (% VDD)   |

| 1, 9, 17, 25  | 10    | 0.20  | PMOS      | 60        |

| 2, 10, 18, 26 | 10    |       |           |           |

| 3, 11, 19, 27 | 50    |       |           |           |

| 4, 12, 20, 28 | 30    |       |           |           |

| 5, 13, 21, 29 | 200   | 0.58  | NMOS      | 100       |

| 6, 14, 22, 30 | 450   |       |           |           |

| 7, 15, 23, 31 |       |       |           |           |

| 8, 16, 24, 32 | 750   |       |           |           |

#### 2.3.2 Analysis of injected TF effects

The injection of single TFs on  $D_{<1>}$  is able to induce four effects :

- (1) TFs that completely overlap the sampling window always produce a SE in the DFF [84];

- (2) TFs that rise and fall inside the sampling window are either masked or they cause a DE or a SE;

- (3) TFs that partially overlap with the sampling window provoke a  $CLK \rightarrow Q$  time variation, i.e. a DE;

- (4) TFs that do not overlap with the sampling window are always masked [84].

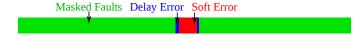

In order to evaluate the proposed scenarios in function of the time and their consequences, Fig. 2.6 defines three color bars that represent the instants at which a single TF starts to be injected:

- (1) Green color bar: Masked Fault (MF): the injected single TF do not perturb the output Q of the monitored DFF, i.e. no SE is induced;

- (2) Blue color bar: Delay Error (DE): the injected single TF increases the  $CLK \rightarrow Q$  delay of the DFF more than 10% in relation to the typical  $CLK \rightarrow Q$  delay under no TF effects;

- (3) Red color bar: Soft Error (SE): the injected single TF provokes a SE.

Fig. 2.6: Definition of color bars for MFs (green), DEs (blue) and SEs (red).

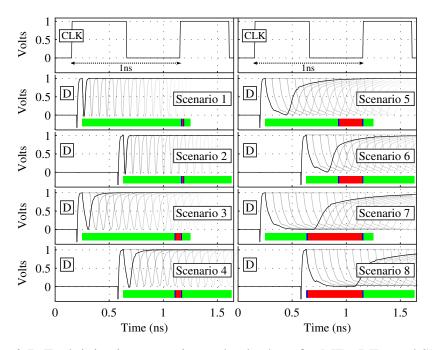

Figure 2.7 shows, for each scenario the clock signal CLK, the monitored data signal  $D_{<1>}$  and the color bars representing the behavior of eight scenarios regarding the TF profile. Note that, due to the different slack values provided, the TF for each scenario had its beginning at a specific time, e.g., for scenario 1, the TF begins at 0.2 ns, the same instant in which the signal  $D_{<1>}$  reaches its high voltage level (1 V), however, for scenario 2, the TF begins at 0.58 ns since, due to the different slack, signal  $D_{<1>}$  has its high voltage level at this time. For the others scenarios, the same principle applies, i.e., for each scenario there is a difference in the slack time provided, in the TF polarity, in the width, or in the amplitude of the TF. It can be

noted that the number of SEs caused in each scenario is highly dependent on the width of the injected transient fault.

Fig. 2.7: Fault injection scenarios and color bars for MFs, DEs, and SEs.

#### 2.3.3 Evaluation metrics

Figures of merit are defined herein to better compare and to quantify effectiveness of the CED techniques. For a total, for instance, of 1000 single TFs of a scenario, the first metric below measures how many times the CED technique is able to detect the injected single TF:

$$TF_{Detection Ratio} = \frac{\#TF_{detected}}{\#TF_{injected}}.$$

(2.3)

The second and third metrics measure the CED technique effectiveness in detecting injected single TFs that induce, respectively, SEs and DEs:

$$SE_{Detection Ratio} = \frac{\#SE_{detected}}{\#SE_{induced}}.$$

(2.4)

$$DE_{Detection Ratio} = \frac{\#DE_{detected}}{\#DE_{induced}}.$$

(2.5)

The fourth metric measures how many times the CED technique is able to detect a injected single TF that induces a SE or a DE:

$$SE + DE_{Detection Ratio} = \frac{(\#SE + \#DE)_{detected}}{(\#SE + \#DE)_{induced}}.$$

(2.6)

Finally, global metrics are defined by taking into account all the 32 scenarios described in previous subsections, and not only a specific scenario as the evaluation metrics 2.3, 2.4, 2.5, and 2.6 consider. These global metrics are formalized as the arithmetic means of the results over 32

scenarios, or if S is the total number of scenarios and  $X_{Detection Ratio}$  is one of the evaluation metrics 2.3, 2.4, 2.5, and 2.6, we have:

$$X_{Detection Ratio Global} = \frac{\left(\sum_{i=1}^{S} X_{Detection Ratio[i]}\right)}{S}$$

(2.7)

#### 2.4 Simulation results and comparative analysis

Simulation results and comparative analysis of the CED techniques described in previous sections are provided herein by using the proposed evaluation method detailed in section 2.3.

#### 2.4.1 Description of simulation experiments

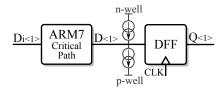

In order to simulate the effects of single TFs on a complex system, the critical path of an ARM7 processor – designed in a commercial CMOS FD-SOI 28-nm technology – has been extracted as this is potentially the critical part of the system. Fig. 2.8 summarizes the extracted data path represented by the ARM7 Critical Path block connected to the input  $D_{<1>}$  of a DFF.

Two current sources are shown in Fig. 2.8 because depending on the input  $Di_{<1>}$  of the ARM7 Critical Path block, the injected transient current will follow a path from the NMOS sensitive drain to its p-well bulk or from the PMOS sensitive drain to its n-well bulk.

Fig. 2.8: Simulated circuit: a critical path of an ARM7 processor in a commercial CMOS FD-SOI 28-nm technology.

#### 2.4.2 Comparative analysis for scenario 5

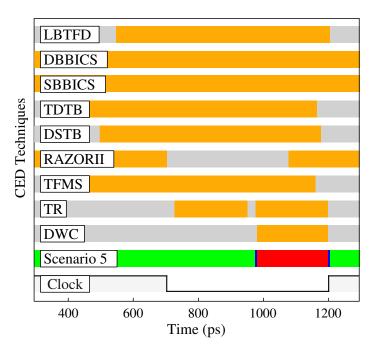

Comparative results are analyzed in this subsection for scenario 5 of the method described in section 2.3, i.e. TFs on NMOS with 200 ps of width and amplitude of VDD, cf. Table 2.1. Fig. 2.9 shows the instants at which a TF with such a profile starts to be formed and a CED technique is able to detect it (orange) or not (light gray). The rising edge of the clock happens at 1.2 ns. The orange color means, therefore, the error signal of the CED scheme raised, and the light gray color means the opposite. Each row of Fig. 2.9 is composed of 1000 simulated points, meaning that 1000 simulations were performed for each scenario and for each CED technique. Taking as example the results of the DWC scheme in Fig. 2.9, the DWC's error signal is raised only when a TF reaches the monitored memory element causing a SE. Consequently, the orange part matches with the red one. For the proposed scheme (LBTFD), note in Fig. 2.9 that the error signal is raised when there are transitions within the detection window, which has been calibrated to accommodate TFs with width up to 450 ps. Therefore, the LBTFD's error signal is also raised at instants when there is no occurrence of soft error.

Fig. 2.9: Detection results regarding scenario 5.

#### 2.4.3 Global comparative analysis

Simulation results for each CED technique regarding its effectiveness in detecting single TFs as well as its total power consumption are provided in Table 2.2. For a global comparative analysis, Table 2.2 present results that take into account all the 32 scenarios, i.e. the global metrics detailed in subsection 2.3.3. If a CED technique, for instance, works better in scenario 1 than scenario 3, Table 2.2 is not suitable to analysis it. However, as the aim of this work is also to provide an insight of the global effectiveness of a CED technique in different scenarios of TFs, Table 2.2 is a great asset to it.

Note in Table 2.2 the results of the TFMS technique, it shows that 87.39% of SEs and 44.97% of DEs were detected, meanwhile the proposed technique LBTFD – aiming mainly the

| CED<br>Technique | Power (μW)  | $rac{\mathrm{TF_{detected}}}{\mathrm{TF_{injected}}}$ | $rac{	ext{SE}_{	ext{detected}}}{	ext{SE}_{	ext{induced}}}$ | $\frac{\mathrm{DE_{detected}}}{\mathrm{DE_{induced}}}$ | $\frac{(\text{SE+DE})_{\text{detected}}}{(\text{SE+DE})_{\text{induced}}}$ |

|------------------|-------------|--------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------|

| DWC [115]        | > 100 %     | 16.69 %                                                | 100.00 %                                                    | 0.34 %                                                 | 28.87 %                                                                    |

| TR [93]          | 3.86 /bit   | 23.64 %                                                | 74.47 %                                                     | 16.04 %                                                | 33.16 %                                                                    |

| SBBICS [34]      | 6.56        | 100.00 %                                               | 100.00 %                                                    | 100.00 %                                               | 100.00 %                                                                   |

| DBBICS [121]     | 5.65        | 94.23 %                                                | 100.00 %                                                    | 94.75 %                                                | 96.38 %                                                                    |

| RAZORII [29]     | 199.21 /bit | 43.70 %                                                | 72.53 %                                                     | 37.82 %                                                | 47.95 %                                                                    |

| TDTB [12]        | 3.32 /bit   | 77.98 %                                                | 95.54 %                                                     | 75.32 %                                                | 81.49 %                                                                    |

| DSTB [12]        | 3.26 /bit   | 47.02 %                                                | 83.70 %                                                     | 45.25 %                                                | 56.94 %                                                                    |

| TFMS [113]       | 3.02 /bit   | 50.50 %                                                | 87.39 %                                                     | 44.97 %                                                | 57.92 %                                                                    |

| LBTFD [this]     | 2.64 /bit   | 57.17 %                                                | 100.00 %                                                    | 100.00 %                                               | 100.00 %                                                                   |

Table 2.2: Total power and effectivenness of the CED techniques under analysis

detection of SEs – was able to detect 100% of the injected TFs that result in SEs. Otherwise, if the TF width is longer than the designed DW, a few SEs will pass undetectable by LBTFD. Results are interesting if compared to the other CED techniques. Moreover, the design of the proposed LBTFD is easier than BBICS-based techniques because only standard cells can be used, implicating directly in less time to conceive the circuit. Although SBBICS was able to detect 100% of the injected TFs, it is not a known standard cell and requires to partition the substrate into islands with separated n-well and p-well regions.

#### 2.5 Conclusions

A technique capable to detect TFs has been presented and analyzed in this chapter. Furthermore, a simulation-based method for classifying and evaluating CED techniques has been defined. For the target scenarios of the method, the proposed CED technique is able to detect all the TFs that result in SEs or DEs in the DFF. The evaluation method takes into account only single TFs that survive the attenuation of logical or electrical masking effects in order to compare exclusively the effectiveness of the different CED techniques – and not the ability of target combinational circuits in masking TFs. This evaluation strategy allows, therefore, to quickly analyze a CED technique independently of the logic complexity of the system. Results in Table 2.2 enable designers to choose the CED technique (or techniques) that suit best for their purposes.

#### Chapter 3

### Architectures of body built-in current sensors for detection of transient faults

Among the many design strategies for detection of transient faults caused by radiation or optical sources, Bulk or herein Body Built-In Current Sensors (BBICS) [89] [91] offer a promising solution that is perfectly suitable for system design flows based on CMOS standard cells of commercial libraries [42]. BBICS combine the high detection efficiency of costly fault-tolerance schemes (e.g. duplication with comparison) with the low area and power overheads of less efficient mitigation techniques such as time redundancy approaches [68]. BBICS approach was experimentally validated in bulk CMOS 28-nm and 90-nm chips under the effects of laser sources [11, 19, 133, 146], and designed, moreover, with transistors of carbon nanotubes [111].

In the last 10 years, several BBICS architectures composed of static memories have been proposed [33,34,90,104,106–108,118,119,138,139,145]. In [104], we have compared them in terms of their sensitivities in detecting transient faults. More recently, with the aim of reducing area and power overheads, Simionovski and Wirth devised a new class of BBICS constituted of dynamic memories [120–122]. Unlike previous works and our comparison study in [104], herein we discuss and compare both, static and dynamic, state-of-the-art BBICS architectures, analyzing their area offsets and detection sensitivities in typical and corner conditions. Furthermore, we introduce a new dynamic BBICS architecture with improved detection sensitivity and lower area penalty than its predecessors. The works of this chapter are the perspectives and the sequence of my postdoctoral research activities started at 2011, and within the thesis context of my Ph.D. student Leonel Guimarães, it was published in the international Microelectronics Journal 2017.

Section 3.1 of this chapter classifies and describes the different state-of-the-art BBICS architectures and their basic principles. Section 3.2 presents our new dynamic BBICS architecture, and section 3.3 defines what we call as the sensitivity of a sensor or a memory element in detecting single transient faults. Finally, section 3.4 provides comparative results and analysis of BBICS architectures, and section 3.5 concludes this work highlighting the main BBICS features and perspectives.

#### 3.1 State-of-the-art architectures of built-in current sensors

Built-in current sensors (BICS) were initially proposed as a mechanism for detecting high increases in the current  $I_{DDQ}$  consumed by a CMOS circuit during its quiescent state (i.e. when the circuit is not switching). This type of mechanism enables the testing of CMOS circuits against

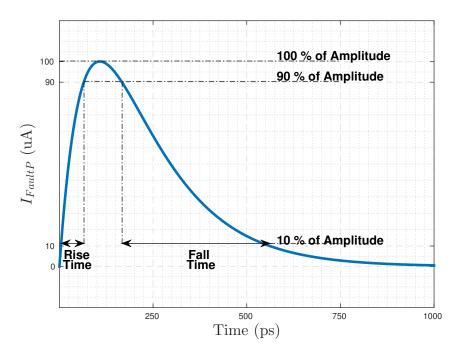

permanent faults [4]. Further, BICS were also adapted for detecting transient faults – anomalous transient currents produced on the circuit by external perturbation sources [137] [80] [17] [120] (Fig. 3.1). Firstly, BICS schemes for identifying transient faults in memory cells (bit flips) were devised [38, 69, 88, 130]. More recently, efforts were made for monitoring transient currents in combinational logic too [87]. All these techniques connect BICS circuits between the sources of the monitored transistors and the power rails (V<sub>DD</sub> or GND), targeting on distinguishing anomalous currents from normal currents. Nevertheless, in today's technologies the amplitude of transient currents induced by radiation effects or fault attacks have the same order of magnitude than currents (source to drain or drain to source) normally generated by switching activities of logic circuits. Hence, schemes monitoring transistor sources are very limited for detecting just a restricted range of transient faults.

For overcoming this BICS problem, Neto et al. proposed in [89] [91] the first architectures of bulk built-in current sensors (BBICS). The major innovation of the BBICS is the connection of sensors between the bulks (i.e., body-ties of the target monitored transistors) and the power rails, rather than applying between the transistor sources and the power rails. Thanks to such a difference, BBICS are able to efficiently detect a wider range of transient faults than the classic BICS.

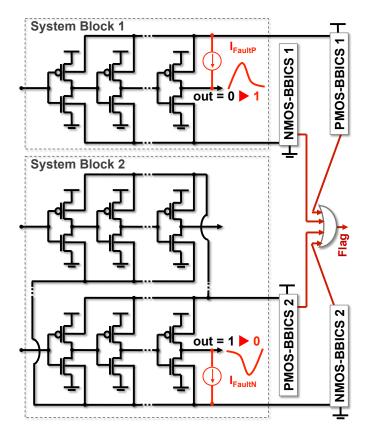

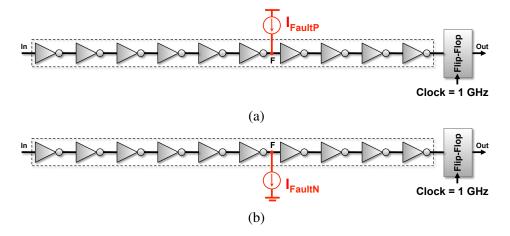

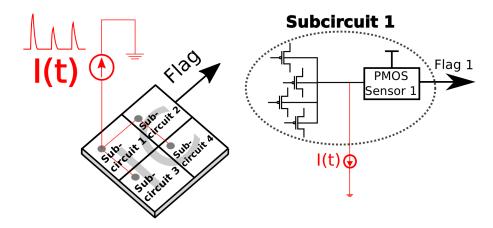

BBICS-based strategy for the protection of a system is illustrated in Fig. 3.2. A pair of sensors is integrated to monitor pull-up and pull-down CMOS networks of the system blocks, hereinafter respectively PMOS-BBICS and NMOS-BBICS. Melo et al. have analyzed in [79] [78] the robustness of BBICS architectures to substrate noise. Wirth in [139] [138] has studied and verified the device-level operation of a BBICS by using TCAD (technology computer-aided design) simulations. In case of an anomalous current such as  $I_{FaultN}$  or  $I_{FaultP}$ , for instance, it will flow through the junction between the bulk and a reversely biased drain of the disturbed transistor (MOSFET "off"), and the sensors will be able to detect it by considering two phenomena:

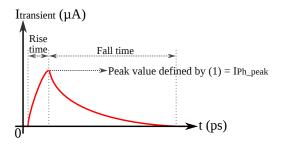

Fig. 3.1: Typical double-exponential profile of a transient fault, which is defined as a transient current generated on the circuit by a external perturbation such as radiation sources or laser beams.

Fig. 3.2: Basic illustrations of BBICS monitoring two system blocks.  $I_{FaultP}$  and  $I_{FaultN}$  are current sources acting as external perturbations that produce abnormal current effects on the circuit defined as transient faults.

- 1. In fault-free scenarios (i.e.,  $I_{FaultP} = 0$  and  $I_{FaultN} = 0$ ), the bulk-to-drain (or drain-to-bulk) current is negligible even if the MOSFET is switching due to a new input stimuli;

- 2. During transient-fault scenarios,  $I_{FaultP}$  or  $I_{FaultN}$  is much higher than the leakage current flowing through the junction.

The sensitivity of a sensor to identify transient faults declines by increasing the number of transistors under monitoring. Hence, target systems have to be split into several blocks that contain a certain number of transistors monitorable by a sensor with sufficient sensitivity in detecting a desired range of transient faults. Fig. 3.2 shows an exemplary system (chains of inverters) divided into two blocks monitored by two pairs of BBICS.

The range of detectable transient faults is adjustable by calibrating the size of some specific transistors of the sensors. Furthermore, BBICS are designed to latch a flag that indicates the detection of the abnormal currents within a defined range representing a risk of consequent soft errors (i.e., bit flips of memory elements).

In according with the latch structure responsible for storing the flag of fault indication, we classify BBICS architectures into static and dynamic. Static BBICS, which contain a static memory cell, are able to monitor transient faults independently of any periodic signal. In contrast, dynamic BBICS feature a dynamic memory, which requires by nature a periodic refresh signal to eliminate harmful leakage effects on its voltage output. In the following subsections, we summarize the state-of-the-art BBICS architectures in four types of static sensors and one type of dynamic sensor.

#### 3.1.1 Single BBICS architectures

The sensor architecture illustrated in Fig. 3.3 is the simplest static BBICS in the literature. It counts only 9 transistors, 4 of which constitute two cross-coupled inverters, i.e., a latch used to register a flag in case of transient faults. This architecture presented in [104] combines concepts proposed in different works [139] [138] [90] [107] [108].

The principle of using a single BBICS circuit to check at the same time both pull-up and pull-down CMOS networks was suggested for the first time in [107] [108] with the aim of saving area. PMOS and NMOS bulk nodes of a single sensor like that in Fig. 3.3 are connected to the monitored body-ties (i.e., bulks of PMOS and NMOS transistors under monitoring) with the help of metal lines. The high ohmic transistors 5 and 7 (with large channel lengths) ensure appropriate voltage bias to the bulks during fault-free scenarios as well as prevent the complete attenuation of the anomalous transient currents in fault contexts. On the contrary, the low-threshold voltage transistors 8 and 6 (with large diffusion widths) are sensing transistors ready to quickly switch in case of transient faults, inverting the latch logic by consequence. This transistor sizing strategy stated in [139] [138] [90] improves the detection sensitivity of the sensor and makes the leakage power overhead negligible.

In order to enhance even more the sensor sensitivity in detecting transient faults, Dutertre et al. [33] [34] propose replacing standard transistors 5 and 7 by high-threshold voltage transistors (HVT), and transistors 6 and 8 by low-threshold voltage transistors (LVT). Dutertre et al. also highlighted in [34] the importance of using triple-well CMOS technology in networks of NMOS transistors monitored by BBICS. This strategy, which embeds NMOS transistors into P-type wells isolated from P-substrate by N-type well implants, increases the robustness of monitored circuits and considerably improves the sensitivity of the sensor in detecting transient faults in pull-down CMOS networks. As the classic N-type wells in PMOS transistors

Fig. 3.3: Single BBICS architecture [104].  $W_{min}$  represents the minimum diffusion width of the transistors,  $L_{min}$  is the minimum channel length, and  $X_n$  and  $X_p$  are design factors used for calibrating the sensitivity of the sensor in detecting transient faults.

of pull-up networks, the P-type wells play in monitored NMOS transistors a role of isolation from P-substrate that efficiently helps BBICS in identifying transient faults in pull-down CMOS networks. LVT and HVT transistors as well as the triple-well feature are provided by most of modern commercial technologies.

Champeix et al. [19] and Borrel et al. [11] have tested a single BBICS architecture in a bulk CMOS 90-nm chip. Moreover, they have performed fault injection campaigns with a laser facility for validating the approach.

#### 3.1.2 BBICS architectures of Neto et al.

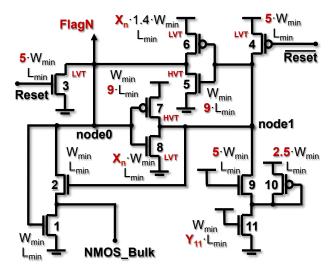

Authors of the first versions of BBICS [89] [91] present in [90] an enhanced architecture formed by a pair of sensors: PMOS-BBICS and NMOS-BBICS. Fig. 3.4 details only the NMOS-BBICS circuit for the sake of simplicity. The illustration omits the PMOS-BBICS and the trimming transistors, which work to compensate process variability in transistors 5 and 7.

The sensor shown in Fig. 3.4 also consists of two cross-coupled inverters that create a latch for fault register. Furthermore, it has additional transistors 9, 10, and 11 acting to increase the sensitivity of the sensor in detecting transient faults. On the contrary, we evidenced in [106] that the leakage power consumption is considerably grown by including these three transistors and using transistors 2 and 5 between NMOS\_Bulk and gnd. As a compensation, a sleep-mode feature dedicated for BBICS is proposed in [106] to reduce the power consumption when the system is left on standby.

Fig. 3.4: State-of-the-art NMOS-BBICS architecture of Neto et al. [90].  $W_{min}$ ,  $L_{min}$ ,  $X_n$ , and  $X_p$  are defined in captions of Fig. 3.3.

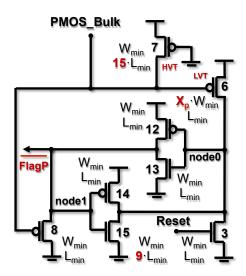

#### 3.1.3 BBICS architectures of Zhang et al.

Zhang et al. [145] propose architectural improvements to BBICS of Neto et al. [90] with the intention of eliminating the leakage penalty. The architecture is also formed by a pair of PMOS-BBICS and NMOS-BBICS. Fig. 3.5 shows the PMOS-BBICS devised by Zhang et al. It is operationally similar to its predecessors, excepting by the presence of PMOS transistor 8. The sensor transistors 6 and 7, which make the leakage overhead negligible, were preliminarily

studied and suggested by Wirth [139] [138]. The circuit of the NMOS-BBICS of Zhang et al. is complementary to that illustrated in Fig. 3.5 for the PMOS-BBICS.

The architecture of Zhang et al. [145] has been improved in work [22] with the inclusion of CMOS amplifiers. The function of sensing the transient faults on the bulks is attributed to high-gain CMOS amplifiers, such as the previous works [4, 38, 69, 87, 88, 130] have proposed for monitoring and identifying faults on power rails. Even though an amplifier-based solution seems to be promising in terms of sensitivity in detecting transient faults, the sensor [22] built in a bulk 28-nm chip was experimentally reported in [133] as sensitive to voltage and temperature variations.

Zhang et al. [146] also reported practical results of Fig. 3.5 sensor embedded on bulk CMOS 90-nm chip. The sensor was tested under the effects of laser-based injection sources.

Fig. 3.5: State-of-the-art PMOS-BBICS architecture of Zhang et al. [145].  $W_{min}$ ,  $L_{min}$ ,  $X_n$ , and  $X_p$  are defined in captions of Fig. 3.3.

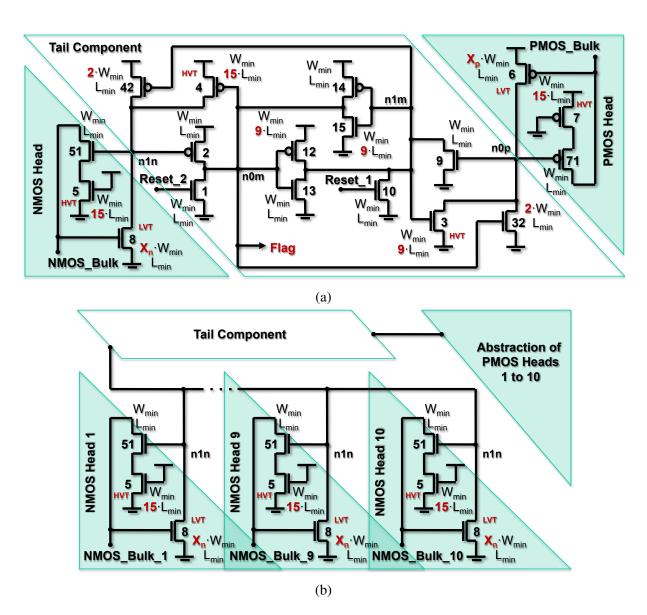

#### 3.1.4 Modular BBICS architectures

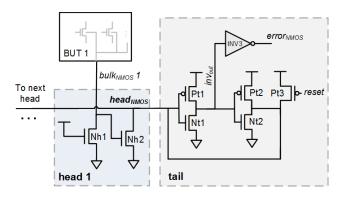

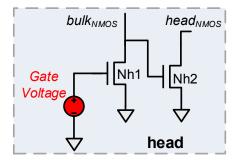

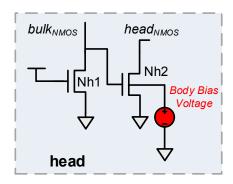

We have presented in [118] [119] an efficient modular technique for reducing the area overhead introduced by BBICS architectures. The idea is to split the sensor into modules named as tails and heads. Fig. 3.6a details this technique applied on a BBICS architecture proposed in [104]. The sensor could be otherwise designed for monitoring the occurrence of transient faults in 10 pull-up and 10 pull-down CMOS networks, for instance; then the architecture will have 10 NMOS heads, 10 PMOS heads, and a single tail circuit shared by them, see Fig. 3.6b. This modular feature is also able to provide process and temperature robustness to the sensors thanks to the use of the several modules spread on the circuit under monitoring [118] [119].

In addition to take benefit from the modular technique, the circuits of Fig. 3.6a architecture [104] have been devised with attributes (operated by transistors 4 and 3) that facilitate the logic inversion of the latch (transistors 12, 13, 14, and 15). Consequently, it considerably improves the sensitivity of the sensor in detecting transient faults. Negligible power penalty is also reported due to the configurations of transistors 5 and 51 as well as 7 and 71, which ensure respectively the bias GND to the P-type wells and  $V_{\rm DD}$  to the N-type wells.

Fig. 3.6: BBICS architecture [104] (a) using modular technique [118] (b).  $W_{min}$ ,  $L_{min}$ ,  $X_n$ , and  $X_p$  are defined in caption of Fig. 3.3.

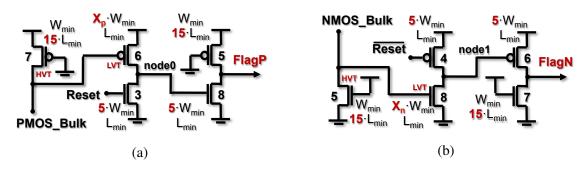

#### 3.1.5 Dynamic BBICS architectures of Simionovski and Wirth

Simionovski and Wirth introduce in [120] the class of the dynamic BBICS architectures. Instead of the conventional latch of the previous static architectures, dynamic memory cells are used for smoothing the switching capacity of the memory node responsible for the fault register. With no feedback circuit wired to the memory node, the sensitivity of the sensor in detecting transient faults is increased and the transistor count of the sensor is reduced. Fig. 3.7 depicts the dynamic circuits featuring the detection of transient faults in pull-up and pull-down CMOS networks.

As any dynamic CMOS circuit, this first version of the dynamic BBICS [120] operates with the help of a reset signal. It periodically refreshes the sensor memory node that is not wired by a feedback circuit. The periodic reset is mandatory to remove accumulative leakage effects on the sensor output, and preventing consequent false indications of fault. Results in [120] show a dynamic BBICS designed on bulk CMOS 130-nm technology is able to properly function by using a short reset pulse with a period of 50 ns. It leaves, therefore, appropriate time for

digital systems deal with the fault indication provided by the sensor in case of transient faults. Simionovski and Wirth [121] have experimentally tested a bulk CMOS 130-nm chip with the sensor presented in Fig. 3.7.

The leakage current effects on the dynamic BBICS have been also studied in [122], and a solution for eliminating the periodic reset signal was presented. The strategy proposes to bias the reset transistors of the sensor for operating in the weak inversion region. Accordingly, a steady very low voltage offset is permanently applied on the place of the periodic reset voltage, ensuring, in fault-free scenarios, a stable operation of the dynamic memory nodes. This important BBICS feature [122] baptized of self reset copes with the former insensitivity of dynamic sensors in detecting transient faults during the short but periodic phases of reset.

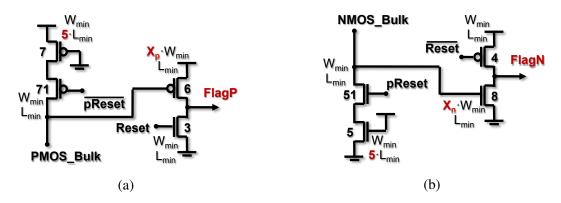

Fig. 3.7: State-of-the-art dynamic BBICS architectures (a) and (b) of Simionovski and Wirth [120] for monitoring transient faults, respectively, in pull-up and pull-down CMOS networks.  $W_{min}$ ,  $L_{min}$ ,  $X_n$ , and  $X_p$  are defined in captions of Fig. 3.3.

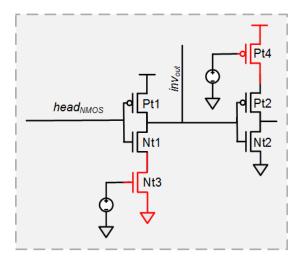

#### 3.2 New dynamic BBICS architecture

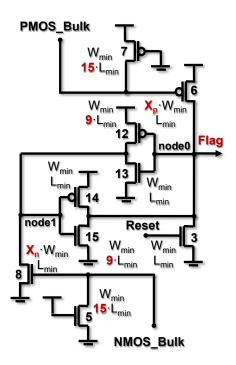

A new dynamic BBICS architecture is presented in Fig. 3.8. The innovations of the proposed BBICS considerably increment the sensor sensitivity in detecting transient faults at expense of negligible power overhead and with lower transistor count than previous architectures.

Fig. 3.8: New dynamic BBICS architectures (a) and (b) proposed in this chapter for detecting transient faults in pull-up and pull-down CMOS networks. The bulks of the PMOS and NMOS transistors under monitoring are biased, respectively, by the voltages on PMOS\_Bulk and NMOS\_Bulk nodes, rather than the voltages on the power rails  $V_{DD}$  and GND.  $W_{min}$ ,  $L_{min}$ ,  $X_n$ , and  $X_p$  are defined in captions of Fig. 3.3.

The new features and differences of the proposed architecture (Fig. 3.8) with regard to the preceding dynamic BBICS [120] illustrated in Fig. 3.7 are:

- 1. In fault-free scenarios, the high ohmic transistors 7 and 5 detailed in Fig. 3.8 are responsible for biasing the bulks of the monitored PMOS and NMOS transistors, which are made more robust with the use of triple-well CMOS technology. Moreover, unlike other BBICS architectures, transistors 71 and 51 (respectively arranged in series with transistors 7 and 5) have the role of temporally including PMOS and NMOS bulk nodes in a floating state that facilitates the switch of the sensing transistors 6 and 8 during scenarios of transient faults. The detection sensitivity of the sensors are, therefore, improved at the cost of a periodic reset (*pReset* in Fig. 3.8 and 3.9) on the gates of transistors 71 and 51, which operate to systematically ensure a suitable voltage bias of PMOS and NMOS bulks.

- 2. The large channel-length transistors 7 and 5 are isolated from the bulks through the minimum-size transistors 71 and 51. The number of parasitic elements connected directly to PMOS and NMOS bulk nodes is thus reduced, and the detection sensitivity of the sensor is enhanced by consequence;

- 3. With the two features described above, the proposed sensor does not need to use special HVT and LVT transistors for obtaining higher detection sensitivity than all previous BBICS architectures;

- 4. Thanks to the large channel-width transistors 6 and 8, the dynamic memory nodes FlagP and FlagN provide steady voltage signals during enough time to be dealt by other system's blocks that have the responsibility of applying recovery actions when transient faults occur;

In addition to the periodic reset pReset, the same conventional reset applied on any BBICS architecture for initializing their memory nodes (Reset in Fig. 3.8) is employed on the gates of transistors 3 and 4. This reset signal can be either periodic such as in dynamic architecture [120] or can feature the self-reset property [122] mentioned in previous section.

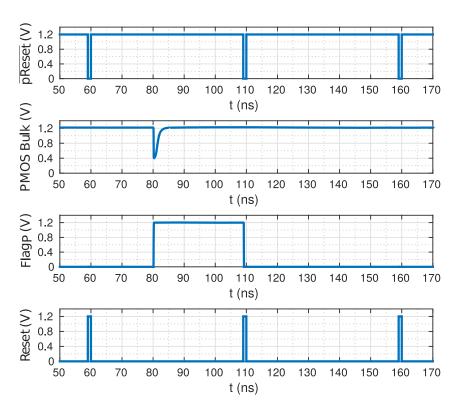

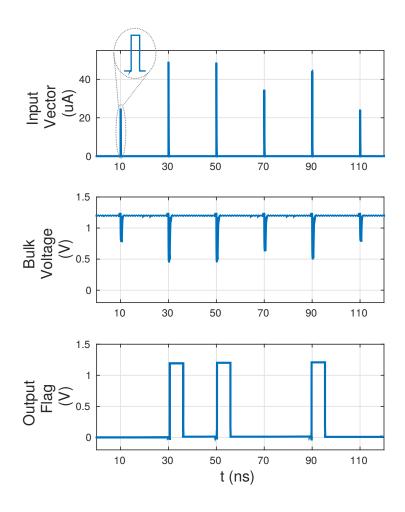

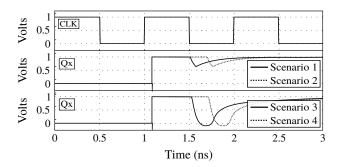

The operation mode of our dynamic BBICS architecture (Fig. 3.8) is illustrated in Fig. 3.9, which details simulation results of a chain of 10 inverters being monitored by a PMOS-BBICS (Fig. 3.8a) and NMOS-BBICS (Fig. 3.8b). The injected single transient fault, represented by the transient voltage glitch on the PMOS bulk node, is successfully detected by the PMOS-BBICS when the sensor's output FlagP goes to  $V_{DD}$ . The pulse on the node Reset is generated by other system's block after the end of the procedure that processes the event of fault indication on the node FlaqP.

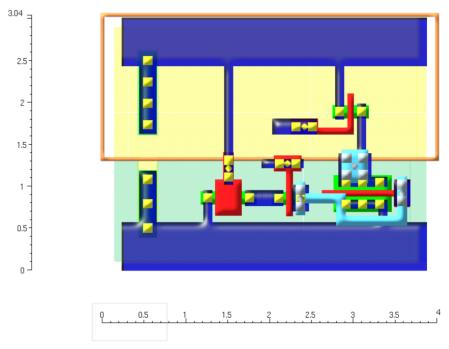

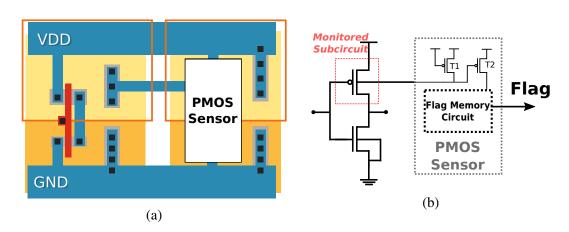

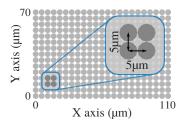

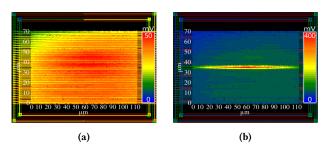

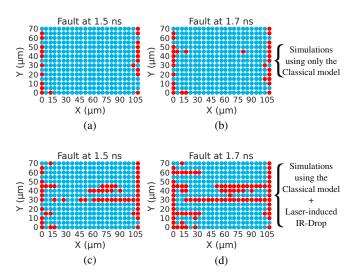

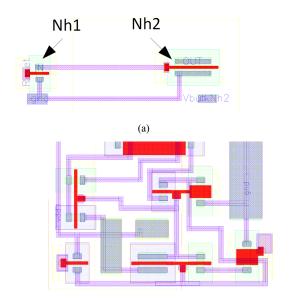

The proposed dynamic BBICS (Fig. 3.8) were designed and verified on a commercial bulk CMOS 65-nm technology. Two cells representing the PMOS-BBICS (Fig. 3.8a) and NMOS-BBICS (Fig. 3.8b) were developed in the same way as the technology's standard cells were designed. The BBICS cells are applicable on the circuit under monitoring by replacing the filler cells that are liable for making the body-ties of the standard cells [33]. The layout of the NMOS-BBICS cell is presented in Fig. 3.10, and its design factors  $X_n$  and  $X_p$  in Table 3.1, which is further explained in section 3.4.

Fig. 3.9: Operation mode of the proposed dynamic PMOS-BBICS detecting the event of a single transient fault on the PMOS bulk node. The fault was injected on a chain of 10 inverters designed on CMOS 65-nm technology.

Fig. 3.10: Layout of the new dynamic NMOS-BBICS cell on CMOS 65-nm technology. The divisions of the dimension axis are in  $\mu m$ . The area of the proposed cell is comparable to the sum of three technology's NAND cells with minimum drive capabilities. The layout design of the PMOS-BBICS cell, which is not illustrated here, is complementary to this figure.

#### 3.3 Sensitivity of a flip-flop in detecting transient faults

Memory elements like flip-flops or latches are sensitive to transient faults that have the capability to reach them and provoke primary transient harmful effects known as: (1) soft errors, which are non-permanent logic inversions of memory elements; or (2) delay errors, i.e. remarkable non-permanent variations on the typical delays of memory elements due to setup time violations.

Soft or delay errors will be produced in the circuit depending on the charge of the transient fault – the integral of the current curve in Fig. 3.1. If an anomalous current has a profile (charge) able to overcome electrical, logical, and latching-window masking effects [55] on a circuit; single or multiple soft errors or delay errors will be generated in memory elements. The smallest anomalous current profile that provokes non-permanent errors (soft or delay errors) is defined in this chapter as the sensitivity of a memory element in detecting transient faults. The threshold at which the memory element becomes sensitive to transient faults is, therefore, the lower bound of the range of transient faults able to induce non-permanent errors in the memory element. The upper bound of this range would be the smallest transient fault that makes permanent errors and can definitely damage the circuit.

#### 3.3.1 Experiments for analyzing the sensitivity of a flip-flop in detecting transient faults

The sensitivity in detecting transient faults of the flip-flops, as numerous and fundamental memory elements of integrated systems, is a significant reference to determine the smallest profiles of transient faults that need to be detected by schemes like BBICS. Hence, we have studied in this work the sensitivity of the smallest flip-flop cell of a commercial CMOS 65-nm technology. The goal is to evaluate and compare it with the sensitivities of different BBICS architectures. Fig. 3.11 illustrates the circuit used as reference in this study. Electrical-level simulations were initially performed with typical conditions, nominal Vdd (1.2 V), 25 °C, and standard threshold voltage (SVT) transistors. The technology's smallest sized standard cells with parasitic elements were applied with the purpose of creating the circuit conditions that produce the smallest profiles of transient faults.

Fig. 3.11: Reference circuits of this study: chains of 10 inverters with a flip-flop. It is designed with the target technology's smallest standard cells with the aim of identifying the smallest profiles of transient faults ( $I_{FaultP}$  and  $I_{FaultN}$ ) detectable by a flip-flop.

The influence of several different profiles of single transient faults was investigated on the reference circuits (Fig. 3.11) by using the classical transient-fault model for CMOS circuits [137] [80] that is detailed in [17] and [120]. The faults were electrically simulated by injecting either a double exponential current source  $I_{FaultP}$  or  $I_{FaultN}$  (Fig. 3.1) on the technology's most sensitive drain node, which is the drain with the lowest capacitance – i.e. node F (Fig. 3.11) between two inverter cells with the smallest dimensions in the technology's standard cell library.

Different profiles of single transient faults were injected by adjusting different current amplitudes and fall times on the parameters of  $I_{FaultP}$  (or  $I_{FaultN}$ ). The rise times were always set on the order of 5 ps to keep the typical shapes of transient faults: short rise time and longer fall time [32] [36]. Several electrical-level simulations were thus done by sweeping the parameters of  $I_{FaultP}$  (or  $I_{FaultN}$ ) up to find the smallest profiles of single transient faults that propagate through the inverters and provoke a soft error or a delay error in the flip-flop. In this study we consider as a delay error any flip-flop's typical delay variation that is higher than 10 %. In addition, as the shape of a transient fault is technology and event dependent, the sweep of the parameters of  $I_{FaultP}$  (or  $I_{FaultN}$ ) was limited to not create voltage amplitudes higher than 110 % of Vdd. This strategy prevents the injection of voltage peaks that could lead the circuit to permanent errors or out of the technology's specifications.

## 3.3.2 Results and analysis of the sensitivity of a flip-flop in detecting transient faults

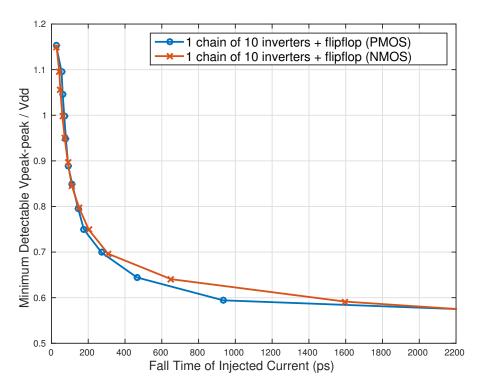

Fig. 3.12 shows the electrical-level simulation results of the circuits in Fig. 3.11. The vertical axis represents the minimum peak-to-peak voltage (on node F and normalized to Vdd) that is detectable by the flip-flop after  $I_{FaultP}$  (or  $I_{FaultN}$ ) is injected with a fall time defined in the horizontal axis. For instance, if  $I_{FaultN}$  is applied on node F with a fall time of 200 ps (measured between 90 % and 10 % of the injected current amplitude), the resulting minimum detectable peak-to-peak voltage on node F is around 0.9 V (i.e. 75 % of 1.2 V). The flip-flop will thus suffer a soft or delay error if a single transient fault with 200 ps of fall time produces a peak-to-peak voltage on the node F greater or equal to 0.9 V. Fig. 3.12 allows, therefore, identifying the range of single transient faults that reach and produce non-permanent errors in the flip-flop. Note that single transient faults making peak-to-peak voltages on the order of 57 % of Vdd are still able to provoke soft or delay errors; however they require very long fall times to accomplish it (approximately 2200 ps).

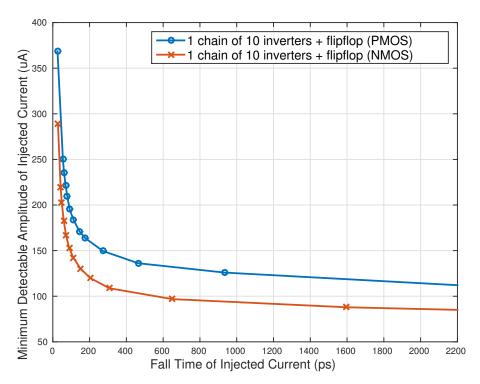

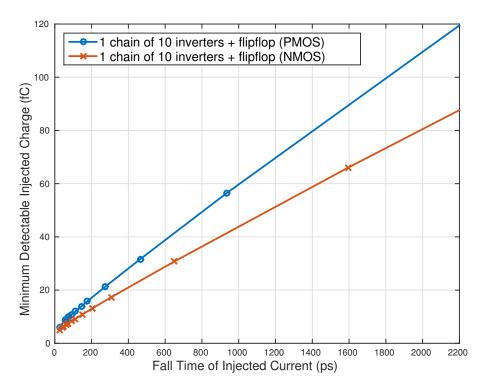

Fig. 3.13 and Fig. 3.14 detail the smallest profiles of transient faults ( $I_{FaultP}$  and  $I_{FaultN}$ ) that produce the peak-to-peak voltages of Fig. 3.12. Thereby, a single transient current injected into node F with a fall time of 200 ps needs at least an amplitude of nearly 120  $\mu$ A (NMOS case) or 160  $\mu$ A (PMOS case) to provoke a soft or delay error in the flip-flop. In Fig. 3.14, the respective minimum detectable injected charges (critical charges), which correspond the areas of the injected current curves (Fig. 3.1), are presented on the order of 13 fC (NMOS case) and 17 fC (PMOS case).

## 3.4 Analysis and comparison of BBICS sensitivities in detecting transient faults

This section analyzes previously discussed state-of-the-art BBICS architectures in terms of their sensitivities in detecting transient faults. In addition, we compare them with the dynamic BBICS proposed in this chapter.

Fig. 3.12: Minimum peak-to-peak voltages (on node F and normalized to Vdd) that are detectable by a flip-flop (Fig. 3.11) after the injection of single transient faults ( $I_{FaultP}$  or  $I_{FaultN}$ ) with fall times between 10 ps and 2200 ps; and a rise time on the order of 5 ps.

Fig. 3.13: Minimum current amplitudes (injected on node F) that are detectable by a flip-flop (Fig. 3.11). The related injected currents, in function of different fall times (horizontal axis), create the peak-to-peak voltages illustrated in Fig. 3.12.

Fig. 3.14: Minimum charges (injected on node F) that are detectable by a flip-flop (Fig. 3.11). The related injected currents, in function of different fall times (horizontal axis), create the peak-to-peak voltages illustrated in Fig. 3.12.

### 3.4.1 Experiments for sizing BBICS architectures

All BBICS architectures were electrically simulated monitoring chains of 10 minimum-sized inverters under the same conditions of experiments described in section 3.3.

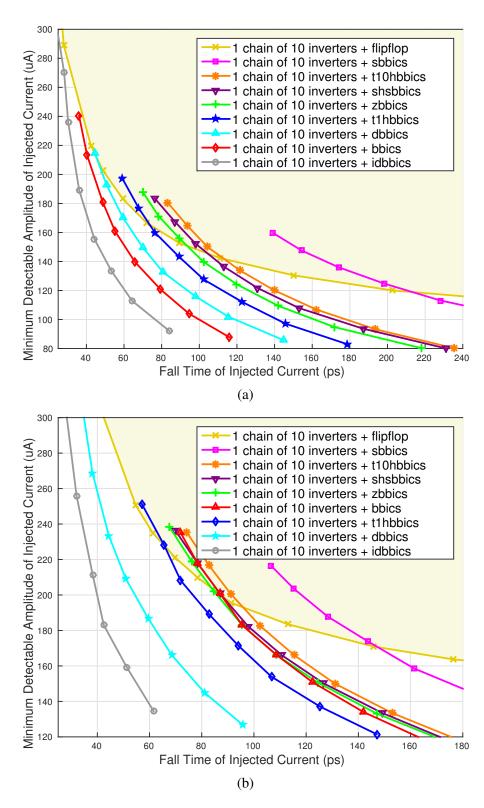

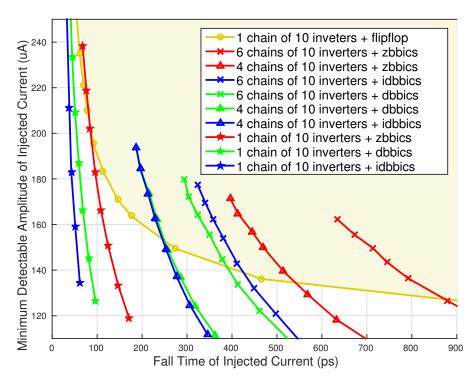

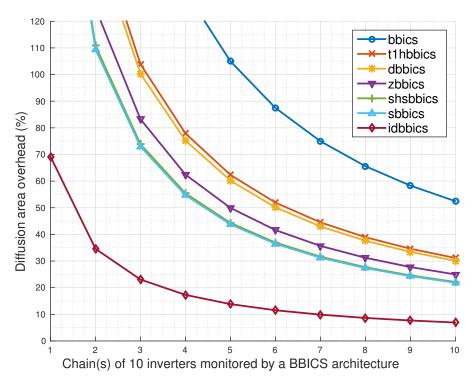

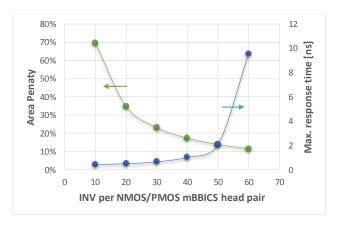

BBICS in Fig. 3.3 is denominated herein as "sbbics", and its improved version (using HVT transistors instead of SVT transistors 5 and 7, and LVT transistors replacing transistors 6 and 8) is defined as "shsbbics". Furthermore, the sensors in Fig. 3.4, 3.5, 3.6a, 3.6b, and 3.7 are named respectively "bbics", "zbbics", "t1hbbics", "t10hbbis", and "dbbics". The dynamic BBICS proposed in this chapter (Fig. 3.8) is labeled with "idbbics". Both NMOS-BBICS and PMOS-BBICS circuits of "bbics", "zbbics", "dbbics", and "idbbics" architectures were taken into account in the analysis of this section.

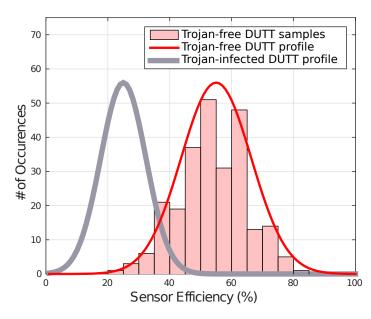

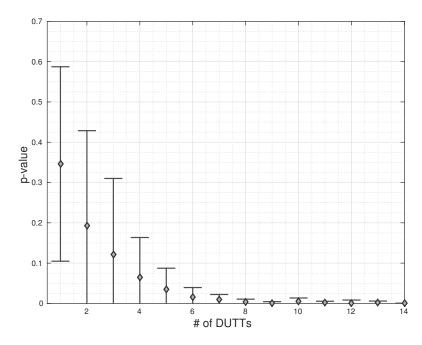

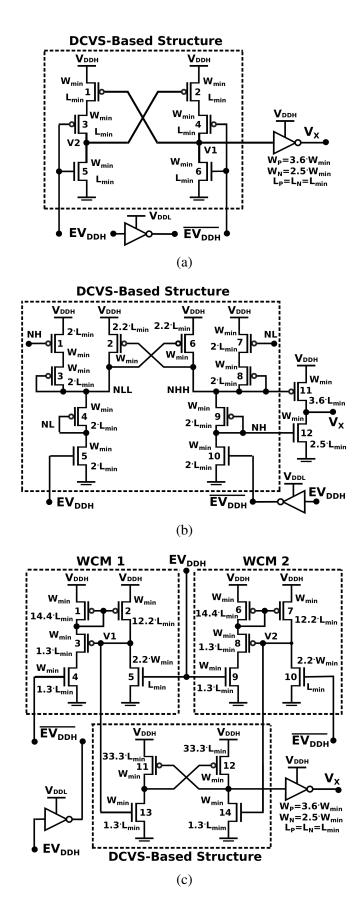

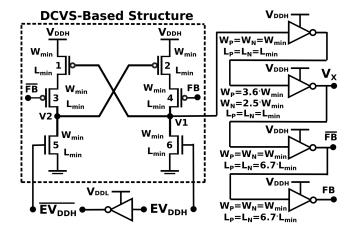

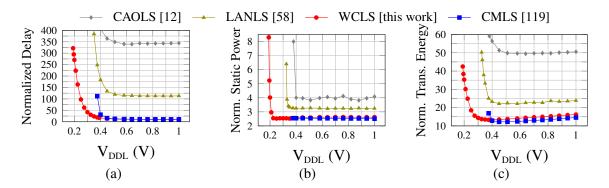

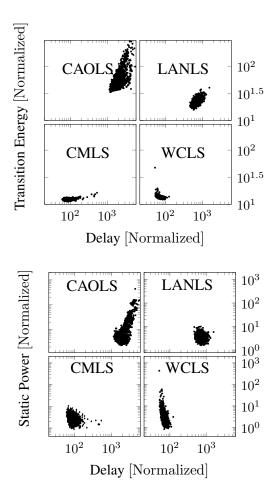

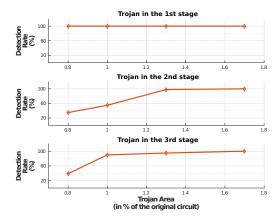

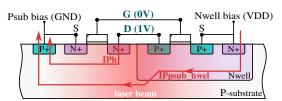

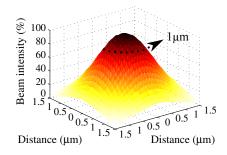

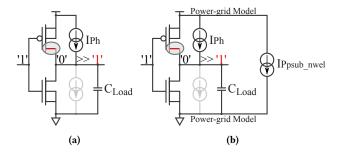

For the "bbics" architecture, we have set  $Y_{11}=9\cdot L_{\min}$  in PMOS-BBICS;  $Y_{11}=45\cdot L_{\min}$  in NMOS-BBICS [90]; and the trimming configuration calibrating the sensors with their best sensitivities in detecting transient faults. The dynamic architectures "dbbics" and "idbbics" were both simulated with a periodic reset pulse of 500 ps repeated each 50 ns (Fig. 3.9). In addition, even though the original circuit propositions of "bbics" [90], "zbbics" [145] [146], and "dbbics" [120] [121] do not mention the use of LVT and HVT transistors for improving the sensor sensitivity [33] [34], we have used them in the simulated designs of this experiment in order to perform the full potential of such BBICS architectures. Original architectures "zbbics", "bbics", and "dbbics" were, therefore, also enhanced with LVT and HVT transistors in the same way of the other state-of-the-art BBICS analyzed in this chapter with the aim of making a fair comparison of their sensitivities in detecting transient faults. In the proposed "idbbics" architecture, nevertheless, LVT and HVT transistors are not required to calibrate competitive sensitivity, then only SVT transistors were used.