# Development of Nanopillar Arrays Nanopatterning Without Lift-Off for Transferable GaN-Based $\mu$ LEDs

Nabil Labchir, Saber Hammami, Kilian Baril, Maya Wehbe, Sebastien Labau, Jerome Reche, Camille Petit-Etienne, Marie Panabière, Pierre-marie Coulon, Blandine Alloing, et al.

# ▶ To cite this version:

Nabil Labchir, Saber Hammami, Kilian Baril, Maya Wehbe, Sebastien Labau, et al.. Development of Nanopillar Arrays Nanopatterning Without Lift-Off for Transferable GaN-Based  $\mu \rm LEDs.$  Advanced Materials Technologies, 2024, 10.1002/admt.202400166 . hal-04625869

# HAL Id: hal-04625869 https://hal.univ-grenoble-alpes.fr/hal-04625869v1

Submitted on 8 Nov 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Development of Nanopillar Arrays Nanopatterning Without Lift-off for Transferable GaN-Based µLEDs

Nabil Labchir <sup>1,2</sup>, Saber Hammami <sup>2</sup>, Kilian Baril <sup>3</sup>, Maya Wehbe <sup>3,4</sup>, Sebastien Labau <sup>1</sup>, Jerome Reche

<sup>2</sup>, Camille Petit-Etienne <sup>1</sup>, Marie Panabière 1, Pierre-Marie Coulon <sup>3</sup>, Blandine Alloing <sup>3</sup>, Daniel Pino Munoz <sup>4</sup>, Jesus Zuniga-Perez <sup>3,5</sup>, Patrice Gergaud <sup>2</sup>, Matthew Charles <sup>2</sup>, Cécile Gourgon <sup>1</sup>

<sup>1</sup> Université Grenoble Alpes, CNRS, CEA/LETI-Minatec, Grenoble INP, LTM, 17 Rue des Martyrs, Grenoble 38054, France

<sup>2</sup> Université Grenoble Alpes, CEA-LETI, 17 Rue des Martyrs, Grenoble 38054, France

<sup>3</sup> Université Cote d'Azur, CRHEA-CNRS, Rue Bernard Gregory, Valbonne 06560, France

<sup>4</sup> MINES Paris, PSL Univ., Centre de mise en forme des matériaux (CEMEF), CNRS, CS 10207 rue Claude Daunesse, 06904 Sophia Antipolis, France

<sup>5</sup> MajuLab, International Research Laboratory IRL 3654, CNRS, Université Cote d'Azur, Sorbonne Université, National University of Singapore, Nanyang Technological University, Singapore, Singapore

Corresponding author: nabilllebchir@gmail.com

The mass production of µLEDs requires an upscaling approach on 200 mm wafers, which implies the deployment of a technology that achieves zero defectivity without liftoff. In this report, Nanoimprint lithography (NIL) processing has been successfully optimized for nanostructuring GaN-based Silicon-On-Insulator (SOI) substrates. The etching of SiO<sub>2</sub>/GaN/AlN/Si/SiO<sub>2</sub> layers using different plasmas is conducted and multi-layer nanopillars 100-200 mm in diameter have been fabricated. This approach generates zero-defect arrays of pillars, which is particularly advantageous for the growth process. In addition, the SiO<sub>2</sub> at the bottom of the pillar allows it to twist during the subsequent GaN regrowth, as this layer becomes soft at the growth temperature >1000°C. This ability to deform enables a coalescence of pillars into layers with reduced dislocation density. As a result, high quality GaN microplatelets and µLEDs were grown via a bottom-up approach based on pendeoepitaxy using metal organic vapor phase epitaxy (MOVPE). The fabricated µLEDs have a very smooth surface with a roughness of 0.6 nm which facilitated the implementation of an easy and simple transfer protocol. Adhesive tape and metal-metal bonding, were used to bond the µLEDs onto a metal-coated silicon substrate. The reported findings in this study are highly encouraging and offer exciting new insights into the development of the next generation of high-performance displays.

#### 1. Introduction

Over the last twenty years, displays have seen a profound evolution and have faced a number of technological issues, including the efficient and independent addressability of individual pixels, the reduction in emitting-region thickness, the increase of display size as well as improving image quality. Today, the issue of energy consumption could lead to the emergence of a new LED-based display technology. Also, the market for microdisplays is in full expansion, with the arrival of new applications that are disrupting the market. In particular, highly luminous microdisplays are required for augmented reality and projection systems. The use of  $\mu$ LEDs should enable the creation of better resolved, compact, low-power, highluminous microdisplays. Consequently, this technology has been the focus of major research efforts in recent years, with the aim of developing innovative materials to meet these technological challenges.<sup>[1-4]</sup>

In this context, gallium nitride (GaN) is being extensively used for the development of microlight emitting diodes (LEDs). However, the optoelectronic behavior and durability of these devices is highly dependent on the point defects incorporated into the active region and on the dislocation density within the GaN heterostructure. These dislocations behave as non-radiative centers, limiting the emitting capacity of such fabricated  $\mu$ LED. Moreover, GaN bulk substrates are very expensive compared with other semiconductors, they are only available in small diameters, and their physical and optoelectronic characteristics are still significantly far from the standards required for successful  $\mu$ LED processing.<sup>[5-9]</sup>

Cost-effective approaches based on GaN thin-film epitaxy on cheaper substrates, such as Si and sapphire, have been developed to circumvent the above-mentioned challenges. <sup>[10,11]</sup> Nevertheless, the epitaxy of GaN on foreign substrates still suffers from several limitations and has not completely eliminated the problems associated with dislocation density due to the large lattice mismatch. In addition, the growth of GaN on Si can lead to the appearance of cracks due to mismatch of thermal expansion coefficients between GaN and Si. One possible solution to prevent the first problem is to reduce the number of epitaxial growth sites in order to reduce the number of dislocations originating from the substrate/nuclei interface. <sup>[12,13]</sup>

Numerous approaches addressing this idea have been developed, such as growth of nanowires, selective and/or anisotropic growth of GaN on patterned substrates with and/or without dielectric masks, e.g. pendeoepitaxy (PE). <sup>[14,15]</sup> However, these strategies have been limited by

the inhomogeneous dislocation density distribution in the GaN that will be used as the active layer for the  $\mu$ LED. This inhomogeneity is due to the misalignment of the crystallites associated to the heteroepitaxial growth before their coalescence. <sup>[16-21]</sup>

For device fabrication, existing optical and/or electronic lithography and plasma etching techniques are able to fabricate surfaces with arrays of  $\mu$ LEDs. However, cathodoluminescence studies have revealed that top down etching of  $\mu$ LEDs creates non-emissive regions at the edges of each fabricated  $\mu$ LED, which greatly reduces the total optical performance of such device. In addition, this process is not suited to obtain freestanding  $\mu$ LEDs, that can be easily transferred to solid or flexible substrates without using highly sophisticated transfer methods.<sup>[22]</sup>

In order to overcome these physical and technological limitations, the growth of GaN crystallites on top of deformable nanopillars could be a promising, powerful and highly innovative solution. This solution has been explored in the last years and a nanoimprint lithography based patterning capability has been established.<sup>[23]</sup> However, this approach requires a lift-off step that is incompatible with 200 mm silicon production lines.

To overcome these limitations, we introduce in the present paper a new approach that does not employ liftoff at any stage, which renders it compatible with 200mm Si production lines. With the newly fabricated nanopillars via nanoimprint lithography and plasma etching, we will implement pendeopepitaxy of high-quality GaN plateletes on SOI substrates, as discussed in references, <sup>[23-25]</sup> and thereafter the growth of complete InGaN/GaN µLEDs. The size of the platelets has been defined so that each one constitutes an individual µLED. These µLEDs will be finally transferred in parallel to a carrier substrate, highlighting the scalability of the whole fabrication/growth/transfer process.

# 2. Results and Discussion

# 2.1 Fabrication of GaN-based nanopillars

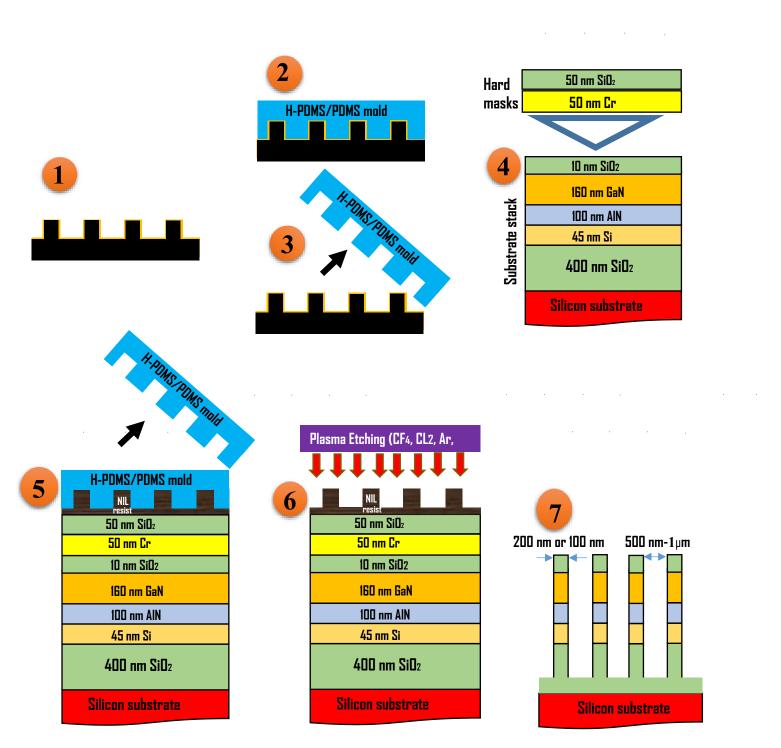

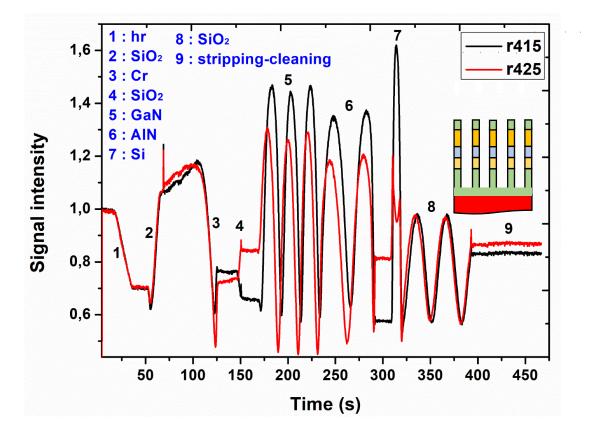

The fabrication of nanopillars using the NIL and plasma etching approach with no-liftoff is a highly successful path for achieving very homogenous etching. Figure 1 illustrates in detail the seven main technological steps of this approach involved in the fabrication of GaN nanopillars. The first phase consisted in fabricating a FDTS coated Si master with the targeted pillar dimensions, i.e. 71 nm in height and 200 nm or 100 nm in diameter distributed within arrays that each measures  $40x30 \mu m^2$ , as illustrated in Figure 1(1) and repeated across the  $36x36 \, \text{mm}^2$  surface. An optical image of the entire mask and an SEM zoomed view showing the hexagonal

distribution of pillars are shown in Figure 2 (a). Subsequently, as shown in Figure 1(2-3), a PDMS/HPDMS composite is deposited on the Si master in order to reproduce the inversed patterns in a flexible mold after the demolding process with a picture of the mold shown in Figure 2-b. We have selected a height of 71 nm in order to imprint the mr6000, measuring 100 nm in thickness, and maintain a residual thickness after the imprint process. The fabrication of the nanopillars from the multilayered GaN on SOI structure requires the deposition of two hard SiO<sub>2</sub> and Cr etching masks, with a Plassys electron beam evaporator, as displayed in Figure 1 (4). The second phase of the process focuses on the nanopatterning via nanoimprint lithography (NIL), which is considered a highly efficient and high-resolution nanotransfer patterning technique [24]. The mr6000, a temperature and UV sensitive resist, is applied to the SiO<sub>2</sub> hardmask surface. Then, an annealing at 95 °C for 3 min takes place, before pressing the PDMS mold onto the annealed resist and carrying out the NIL at a pressure of 1 bar and a temperature of 75 °C in order to crosslink the polymer and successfully transfer the pillar patterns to the polymer (figure 1 (5)). After the NIL and the demolding, we obtain a nanopatterned surface with a residual thickness of the remaining polymer (Figure 1-(6)). The dry etching of the pillars is ensured by combining several plasmas in an ICP DPS reactor (Figure 1(6-7)), and real-time monitoring of the etching process thanks to optical interferometry and measurement of the plasma emission. The monitoring process consists in illuminating the wafer under etching with a xenon lamp at wavelengths ranging from 200 to 800 nm. During etching, curves and bands corresponding to detection wavelengths (415 nm, 425 nm) can be observed. The shape and intensity of each etch-tracking signal depends strongly on the nature of the material under etching.

Figure 1. Fabrication pillars technology: (1) Si master with the FDTS antiadhesive layer, (2) Formation of the H-PDMS/PDMS mold, (3) demolding, (4) deposition of hard masks on the substrate stack, (5) nanopatterning of the resist surface (6) plasma etching of the structure, (7) etched GaNbased nanopillars.

Figure 2. Fabrication of the PDMS mold: (a) image of the Si master and zoomed view of the Si pillars, (b) picture of formed HPDMS-PDMS mold on Si master.

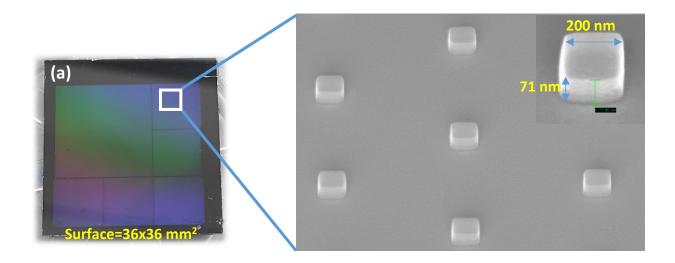

Figure 3 shows the post-NIL pillars and related images of etching steps for the mr6000 residual thickness (rt) and hard masks (SiO<sub>2</sub>, Cr). Controlling this rt after the NIL is an extremely critical step in our approach in order to avoid any definition problems of the nanopillars. The real-time monitoring will be exploited to track the etching in every layer except that of the rt. However, etch monitoring in real time by optical emission is very challenging. Therefore, the total etching time of this rt is carefully optimized and adjusted via several trials. The resulting texture, demonstrating the formation of PDMS pillars on the surface after NIL, is highlighted in Figure 3-a-b. The remaining resist was then etched with a plasma consisting of O<sub>2</sub> (30 sccm), Cl<sub>2</sub> (40 sccm), and Ar (80 sccm) for 40 s until reaching the SiO<sub>2</sub> surface as observed in Figure 3-c. Removing any residual traces of mr6000 from the surface is a critical point for avoiding any subsequent inhomogeneity in the etching process. The first SiO<sub>2</sub> etch mask was etched using a

CF<sub>4</sub>-based plasma (100 sccm). As shown in Figure 3-d, the etching produced a convex profile of the top  $SiO_2$  for the initial pillar formation.

Figure 3. Etching steps of the mr6000 residual thickness (rt) and hard masks (SiO<sub>2</sub>, Cr): (a) typical image of the entire substrate stack with the formed mr6000 pillars on the top after NIL, (b) zoomed view on the rt of the mr6000, (c) after etching of the rt, (d) SiO<sub>2</sub> and (e) Cr.

Next, a plasma based on Cl<sub>2</sub> (100 sccm) and O<sub>2</sub> (40 sccm) was employed to etch the Cr etch mask down to the SiO<sub>2</sub> surface deposited on GaN. This SiO<sub>2</sub> layer will be used for the masked

pendeoeptaxy in order to block the threading dislocations from the pillars and prevent their propagation in the GaN platelet, which will be used as templates for the subsequent growth of  $\mu$ LEDs.<sup>[25]</sup> Figure 3-d shows that the etching process forms a Cr-based profile that will be transferred to the GaN/AlN/Si/SiO<sub>2</sub> substrate stack for fabricating GaN-based nanopillars. This profile ensures the control of the pillar diameters and avoids the widening previously observed due to inclined etching sidewalls.<sup>[24]</sup>

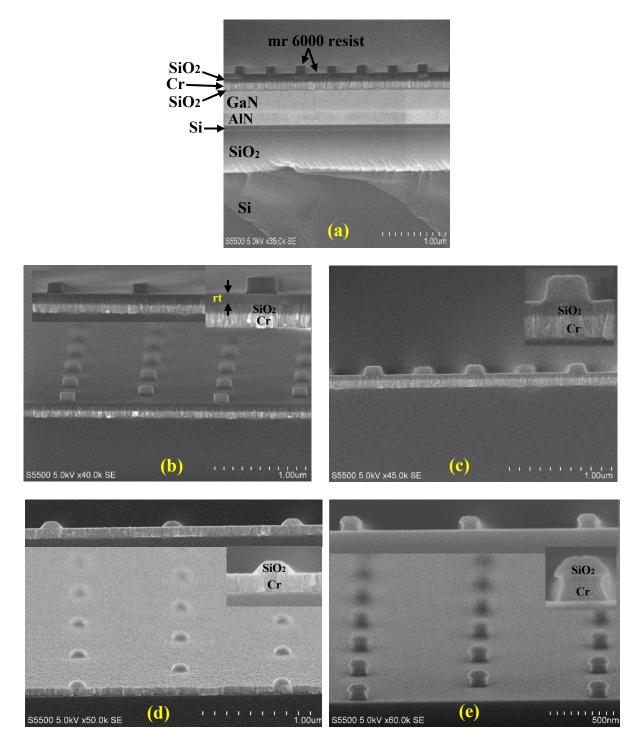

The real-time tracking of each etching sequence during nanopillars development is illustrated in Figure 4. After the three etching steps described in the previous section, we start the etching of the GaN structure with a first etching of the 10 nm SiO<sub>2</sub> by CF<sub>4</sub>-based plasma (step 4). Between each etched layer, we allow 15 s for stabilizing the gas flow. GaN and AlN layers were etched by Cl<sub>2</sub>-based plasma with a gas flow of 80 sccm. As shown in the tracking spectrum, the transition from GaN to AlN is illustrated by the change in oscillation frequency (steps 5 and 6), that corresponds to a change in the etching rate. The Si and 300 nm SiO<sub>2</sub> are etched by CF<sub>4</sub> plasma (steps 7 and 8).

Figure 4. Real-time spectrum monitoring of rt/SiO<sub>2</sub>/Cr/SiO<sub>2</sub>/GaN-AlN/Si/SiO<sub>2</sub> layers etching for fabricating GaN-based nanopillars.

The control of this etching depth is very critical for the GaN pendeepitaxy step. Finally, the etching protocol is terminated by cleaning and stripping using O<sub>2</sub> plasma for 3 min in order to remove any residues from the surface.

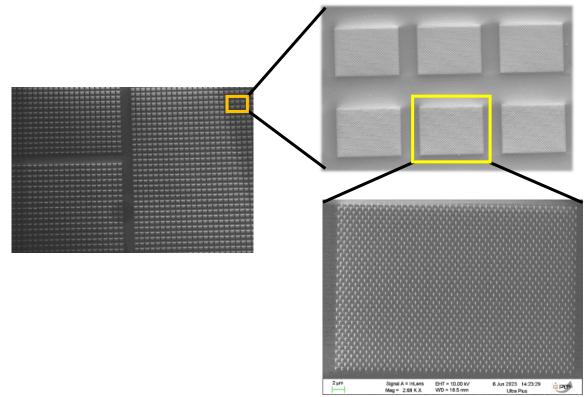

Figure 5 shows a surface area containing several nanopillar arrays. Each array measures 30x40  $\mu$ m<sup>2</sup> and contains pillars measuring 200 nm in diameter. The array is clearly complete, with no missing pillars. This point will be addressed in more detail in the coming section.

Figure 5. Etched nanopillar arrays with no missing or mis-aligned pillar.

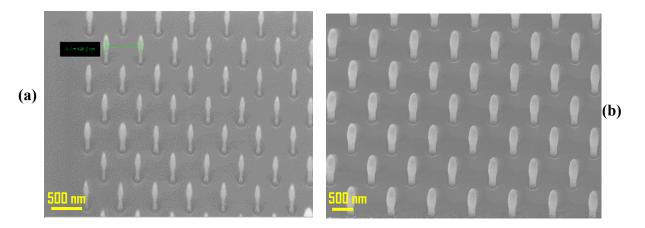

Figure 6. GaN-based nanopillars: (a) 100 nm width pillars, (b) 200 nm width pillars.

In the present report, we have used two Si masters with pillars measuring 200 and 100 nm. Figure 6 illustrates the resulting nanopillars for the two samples after etching. Nano-pillars measuring 100 nm in diameter at the top are shown in Figure 6-a. Thanks to the undercut observed during the Cr etching (Figure 3-e), the pillar diameter is 50 nm at the bottom SiO<sub>2</sub>.

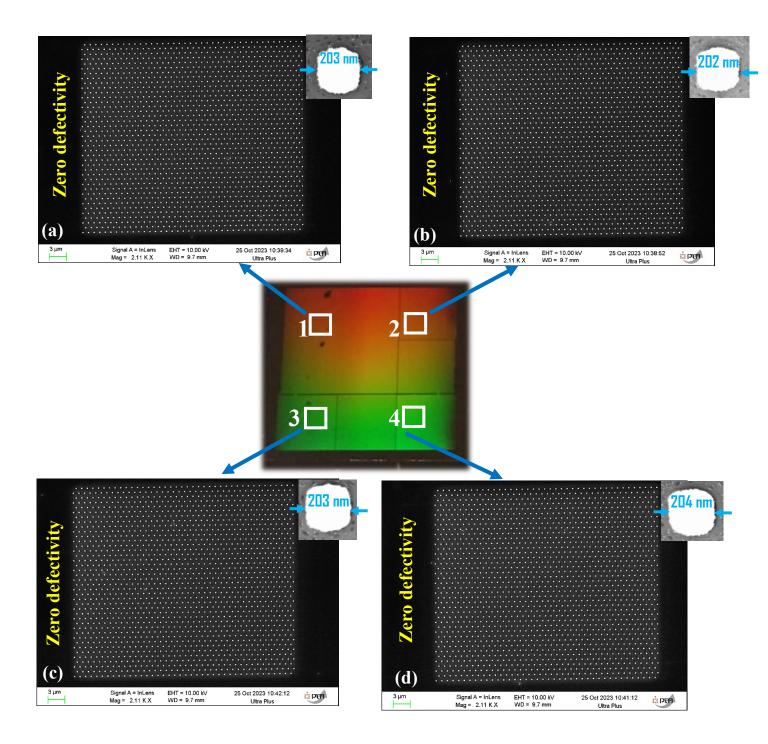

Figure 7. Zoomed views of nanopillar arrays and some measured diameters (a-d) from various zones 1-4 for 36x36 mm<sup>2</sup> etched surface.

All the nanopillars are standing up despite the bottom diameter reduction. Similarly, Figure 6b demonstrates the formation of pillars measuring 200 nm in diameter at the top and 130 nm at the bottom  $SiO_2$  with a pitch of 1 µm. The diameter reduction at the bottom of each nanopillar is an extremely crucial element in our strategy. This profile will facilitate the twisting of  $SiO_2$ based nanopillars during GaN growth on the top of the nanopillars, thanks to the ability of  $SiO_2$ to be deformed at the GaN growth temperature.<sup>[26,27]</sup> Once etching was finished, the sample was placed in a Cr-Etch solution for removing residues of the Cr etching mask.

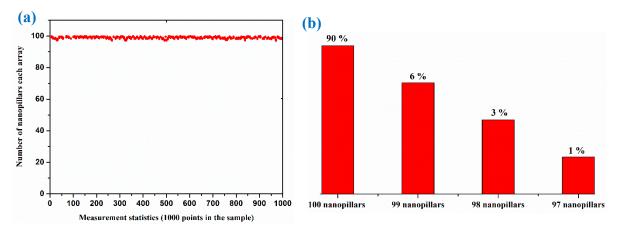

The quality of the grown GaN material depends strongly on the quality of the primary array, since any missing pillar within the array can create a defect during the growth process. It is therefore absolutely necessary to control the patterning process in order to obtain arrays offering an ideal degree of homogeneity. Our initial focus was to investigate the defect rate on pillar arrays with a diameter of 200 nm. Figure 7 shows a uniform nanopillars diffraction image for the 36x36 mm<sup>2</sup> sample and its defect analysis on pillars having a nominal diameter of 200 nm at the top. Four areas were selected from the sample for defectivity investigations. SEM observations in Figure 7 a, b, c, and d showed that every selected zone had a complete array, with no missing pillar indicating excellent etching stability and zero defects. Concerning pillar diameters, the measurements revealed diameters of 200 nm  $\pm$  5 nm at the pillar top, which corresponds to the dimensions of the Si master. To check the accuracy of our approach, another defect characterization study was conducted. This study consisted of scanning 1000 positions in our sample with a pitch of 1 mm. As shown in figures 8-a, the statistics showed that we obtained a number of nanopillars varying between 100 and 97 in each array (a complete array contains 100 nanopillars). The defect histogram (figure 8-b) confirms that 90% of the arrays are complete with zero missing pillars. This study confirms that the defect rate of our approach is very low. Further measurements were performed and the same observations were revealed over the entire surface. These findings confirm the success of the used protocol in fabricating low defect nanopillar arrays on a 3x3 cm<sup>2</sup> surface, which will serve as the starting block for freestanding and easily transferable µLEDs.

Figure 8. Defects characterization.

# 2.2 EDX analysis

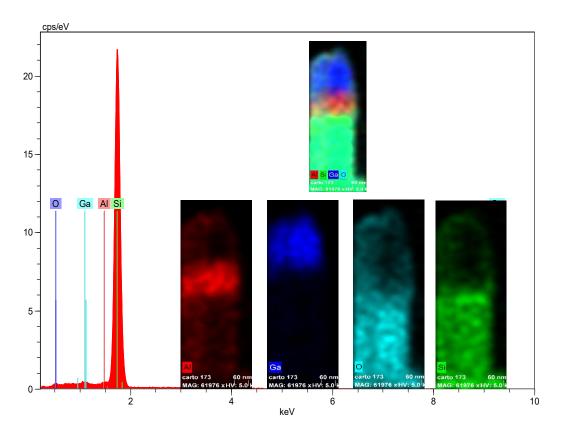

Before the GaN growth, it was checked that there was no residual chrome on the top of the nanopillars in order to avoid any contamination. For this, the elemental composition of nanopillars, measuring 200 nm in diameter and etched 300 nm into the lower SiO<sub>2</sub> layer, was performed using EDX quantitative point analysis and mapping. Figure 9 shows the spectrum of the elemental composition and the individual mapping for each chemical element.

Figure 9. EDX analysis: elemental mapping for an etched 200 nm width pillar and its spectrum.

According to spectrum and individual mapping, we can clearly identify the 10 nm SiO<sub>2</sub> layer deposited on the GaN at the top of the pillar, as well as the other elements of the other layers. No Cr is detected in the spectrum and mapping, which confirms that 40 s in the Cr-Etch is sufficient to remove any remaining Cr hard mask.

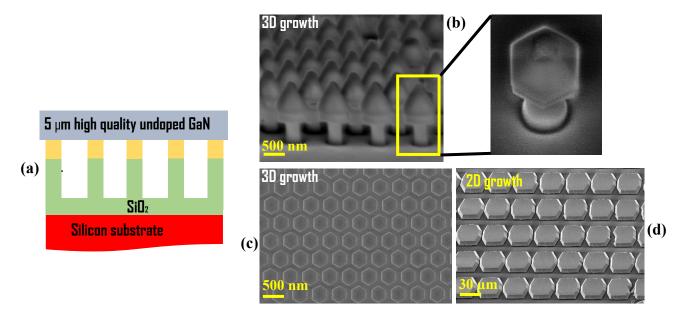

# 2.3 Growth of high quality thick GaN on the top of the nanopillars

As mentioned before, the fabricated nanopillar arrays will be used for GaN and  $\mu$ LED structure growth. Figure 10-a illustrates the growth of GaN on top of SiO<sub>2</sub>-based nanopillars. In this study, we have chosen to focus on nanopillars with 200 nm in diameter. The pendeoepitaxy of high quality thick GaN is conducted through two steps using trimethylgallium (TMGa) and ammonia (NH<sub>3</sub>) as Ga and N source precursors, respectively, and H<sub>2</sub> as carrier gas. In the first step, 3D deposition at 950 °C, 100 Torr is carried out on the top of the nanopillars, forming a pyramid of GaN as shown by the top, zoomed out and cross sectional views in Figure 10 b-c. In this step, the top of the nanopillar behaves as an active growth site. Progressively, the pyramids coalesce through their lateral pyramidal facets.

Figure 10. Growth of GaN platelets: (a) schematic of the grown GaN on the pillars, (b,c) 3D GaN growth on the top of the 200 nm pillars, (d) 2D GaN coalescence on the formed pyramids.

Subsequently, a 2D lateral deposition on the pyramids formed in the first step is processed at 1000 °C, 300 Torr in order to obtain a two-dimensional high quality GaN platelet as shown in Figure 10-d.

# 2.4 Epitaxial growth of µLED structure and its transfer towards carrier substrate

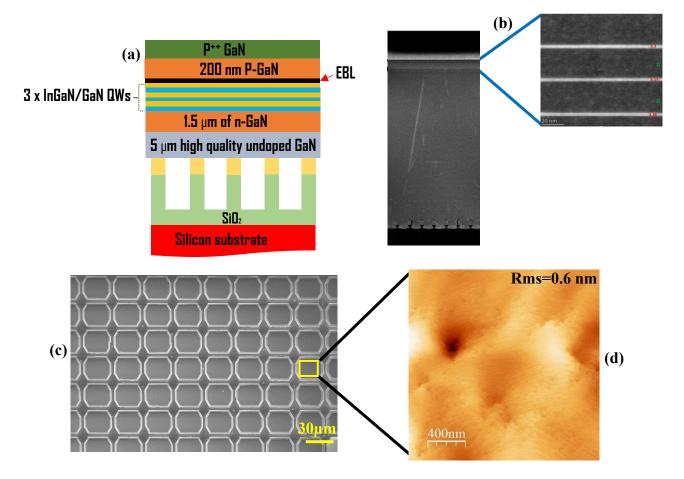

Figure 11 displays a schematic illustration of the  $\mu$ LED structure deposited on the two-stepformed GaN. This  $\mu$ LED structure consists of 1.5  $\mu$ m of n-GaN, 3 alternating InGaN/GaN quantum wells, an electron blocking layer, 200 nm of p-GaN and a highly p<sup>++</sup> GaN layer. The complete structure is shown in cross-sectional TEM in Figure 11-b, with a zoom on the QWs The growth of all these layers results in  $\mu$ LEDs formed on the NIL engineered nanopillars [29].

As mentioned in the introduction, one of the objectives of our bottom-up approach is to transfer  $\mu$ LEDs to solid or flexible substrates. In this context, surface roughness plays a significant role in such processes. A 2x2  $\mu$ m<sup>2</sup> AFM scan of the  $\mu$ LED surface roughness was carried out, and figures 11-c and d demonstrate that the  $\mu$ LED surface is very smooth with an Rms of 0.6 nm.

Figure 11. Epitaxial growth of  $\mu$ LEDs: (a) schematic illustration of the deposited  $\mu$ LED structure on pillars, (b) cross sectional TEM image of the grown  $\mu$ LED structure on GaN pillars and zoomed view of the 3 alternating InGaN/GaN QWs, (c) SEM top view of GaN-based  $\mu$ LEDs, (d) AFM image of the  $\mu$ LED surface.

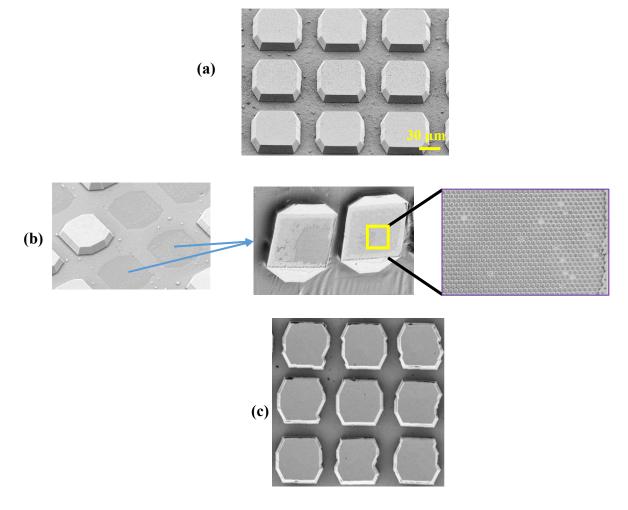

Transferring  $\mu$ LEDs to a carrier substrate is one of the major challenges of active-matrix  $\mu$ displays. The carrier substrate onto which the GaN microLEDs are transferred in the current

study, a metal-coated Si substrate, mimics the CMOS active matrix that will precisely control the desired display  $\mu$ LED. According to the literature, various transfer methods can be used, including flip-chip bonding, transfer by printing, eutectic bonding, metal-metal bonding, laser and chemical debonding.<sup>[28-30]</sup> In our work, we have employed a strategy based on the combination of adhesive tape and metal-metal double bonding in order to enhance the transfer efficiency of  $\mu$ LEDs. The aim of this approach is to highlight a simple and effective transfer procedure. This method consists in first bonding the adhesive tape to the  $\mu$ LEDs then applying a homogeneous force in order to break the SiO<sub>2</sub>-based nanopillars at the bottom of each  $\mu$ LED. Figure 12 shows  $\mu$ LEDs that have been partially collected by the adhesive tape, with a zoomed view showing the back of the  $\mu$ LED. This first part of the transfer is very helpful for getting maximum flexibility to manipulate the  $\mu$ LEDs and create any desired display design. In addition, these  $\mu$ LEDs can be transferred and bonded to a suitable substrate.

Figure 12. transfer of µLEDs: (a) SEM image of as-deposited µLEDs, (b) SEM images after partial transfer of µLEDs, (c) SEM image after total transfer of µLEDs to Si substrate.

For this purpose, a metal-metal bonding is adopted. This means that the  $\mu$ LEDs picked up on tape (Figure 12-b) before being coated with 150 nm of Tin (Sn), while 100 nm of gold is deposited on the Si substrate. Using thermocompression technique and optimizing several parameters such as temperature, pressure and annealing time, we succeeded to transfer the quasi-totality (90%) of  $\mu$ LEDs onto the Si substrate as shown in Figure 12-c. The findings described here and in the previous sections of the paper demonstrate the originality and novelty of our bottom-up approach based on the pendeoepitaxy of  $\mu$ LEDs on the top of 200 nm pillars. This solution offers excellent prospects for the fabrication of future generation  $\mu$ LED displays.

# 3. Conclusion

In this paper, we have established a  $\mu$ LED fabrication process using nano-imprint lithography without lift-off which is large scale and compatible with 200mm silicon photonics platform. For this, a nanopatterning and transfer protocol have been optimized onto GaN on SOI substrates via NIL. Afterwards, the established no-liftoff approach was applied to fabricate GaN/AlN/Si/SiO<sub>2</sub>/Si nanopillars by plasma etching. The resulting nanopillars feature a special profile and a bottom SiO<sub>2</sub> diameter smaller than that of the top. This finding is highly advantageous for promoting the twisting of SiO<sub>2</sub> and thus reducing the dislocation density within the grown GaN. In addition, the developed approach provides nanopillar arrays without defects or missing pillars, and with pillars having diameters of 100 and 200 nm. As a result, freestanding  $\mu$ LEDs were successfully formed on top of nanopillars using a bottom-up approach. AFM scans showed the smoothness of the  $\mu$ LED surface, and these  $\mu$ LEDs were easily transferred onto a silicon substrate by combining adhesive tape and metal-metal bonding steps.

#### 4. Experimental Section

The experimental and fabrication details of nanopillars are illustrated in Figure 1. In this section, an overview of the tools and settings involved in each phase is outlined.

#### GaN on SOI epitaxy:

The GaN-based structure stack used in the present study consists of several layers of materials grown on an SOI substrate formed by bulk Si, 400 nm SiO<sub>2</sub> and 45 nm Si. On top of the SOI, a 100 nm AlN layer is grown to avoid melt back etching and interface defects between the Si and the 160 nm of GaN which is grown on top. The layers are grown by metal organic vapor phase epitaxy (MOVPE) in an AIXTRON close-coupled showerhead (CCS) reactor using trimethylaluminium(TMAI), trimethylgallium (TMGa) and ammonia (NH<sub>3</sub>) as precursors. A

10 nm layer of SiO<sub>2</sub> PVD is deposited on the GaN for masked pendeopepitaxy in the subsequent steps, as detailed in our previous publication on the growth method.<sup>[23]</sup>

# Si master fabrication, antisticking treatment, PDMS mold:

For the nanopatterned surface, the nanostructuration of a 36x36 mm<sup>2</sup> surface of Si substrate was conducted on a Vistec SB0354 electron beam lithography (EBL) machine using a NEB22 resist annealed at 110 °C and its corresponding MF21A developer. Then, the patterns were transferred to Si by dry etching via 50 nm SiO<sub>2</sub> as hard mask using different plasmas based on CF<sub>4</sub>, CL<sub>2</sub>, He-O<sub>2</sub>, HBr gases within an Applied Materials Centura Etch reactor. Then, an antisticking treatment by depositing a 1H,1H,2H,2H-Perfluorooctyltriethoxysilane (FDTS) thin layer is conducted in order to render the Si master surface highly hydrophobic and facilitate the demolding of the cured PDMS mold. This flexible mold is prepared from the FDTS Si master and is ready for NIL patterning experiments.

# NIL patterning:

NIL patterning experiments, for the nanotransfer of mold dimensions into mr6000 resist surface, have been carried out using an EITRE6 Obducat tool using a pressure of 1 bar and temperature of 75 °C.

# **Etching:**

After the nanotransfer by NIL, a 200 mm Applied Materials Centura Etch reactor is deployed for transferring the imprinted patterns through the resin and the SiO<sub>2</sub>/Cr hard masks and then to the GaN layers using our no-liftoff approach via several different plasmas. The etching tracking of each material is conducted using an end-point system of VERITY INSTRUMENTS EYE-D spectrograch.

# Regrowth of GaN and µLED structure:

The  $\sim$ 5µm thick GaN platelet was deposited in two main steps on the top of the nanopillars followed by the growth of the µLED structure which consists of a Si-doped n-GaN layer followed by InGaN/GaN multi-quantum wells, an AlGaN electron blocking layer and a Mg-doped p-GaN top layer.<sup>[23]</sup>

#### Characterization

**Scanning electron microscopy (SEM):** The nanopillars were observed, analyzed and mapped at high resolution using a Zeiss SEM equipped with an EDS detector operating at 10kV acceleration voltage.

Atomic force microscopy (AFM): The  $\mu$ LED topography and surface roughness were examined using a Veeco dimension III AFM in tapping mode.

#### Acknowledgments

The authors would like to thank the French RENATECH network and the Upstream Technological Platform (PTA) for their assistance and technical support. This work was financially supported by the French ANR-20-CE24-0022 PEGADIS project.

#### **Conflict of Interest**

The authors declare no conflict of interest.

#### Keywords

nanoimprint lithography, plasma etching, GaN nanopillars, zero defectivity, pendeoepitaxy,  $\mu$ LEDs.

#### References

- [1] T. Zhan, K.Yin, J. Xiong, Z. He, S. T. Wu, Iscience. 2020, 23, 101397.

- [2] H. J. Jang, J. Y. Lee, G. W. Baek, J. Kwak, J. H. Park, J. Inf. Disp. 2022, 23, 1-17.

- [3] T. Y. Lee, L. Y. Chen, Y. Y. Lo, S. S. Swayamprabha, A. Kumar, Y. M. Huang, H. Kuo,

C. ACS Photonics. 2022, 9, 2905-2930.

- [4] D. Chen, Y. C. Chen, G. Zeng, D. W. Zhang, H. L. Lu, Research. 2023, 6, 0047.

- [5] S. El Badaoui, P. Le Maitre, A. Cibie, F. Rol, S. Litschgi, J. Simon, Y. Le Guennec, 2023 Photonics North. 2023, 1-2.

- [6] P. Li, H. Li, M. S. Wong, P. Chan, Y. Yang, H. Zhang, S. P. Denbaars, Crystals. 2022, 12, 541.

- [7] K. A. Bulashevich, A. V. Kulik, S. Y. Karpov, physica. Status. solidi (a). 2015, 212, 914-919.

- [8] J. J. Wierer Jr, N. Tansu, Laser & Photonics Reviews. 2019, 13, 1900141.

- [9] M. Kodera, A. Yoshioka, T. Sugiyama, T. Ohguro, T. Hamamoto, T. Kawamoto, N. Miyashita, physica. Status. solidi (a). 2018, 215, 1700633.

- [10] S. Dassonneville, A. Amokrane, B. Sieber, J.-L. Farvacque, B. Beaumont, P. Gibart, J. Appl. Phys. 2001, 89 3736.

- [11] O. Nam, T. Zheleva, M. Bremser, R. Davis, J. Electron. Mater. 1998, 27, 233–237.

- [12] T. Zheleva, S. Smith, D. Thomson, K. Linthicum, P. Rajagopal, R. Davis, J. Electron. Mater. 1999, 28, L5–L8.

- [13]U. Schwarz, P. Schuck, M. Mason, R. Grober, A. Roskowski, S. Einfeldt, R. Davis, Phys. Rev. B. 2003, 67, 045321.

- [14] M. Hugues, P.A. Shields, F. Sacconi, M. Mexis, M. Auf der Maur, M. Cooke, M. Dineen,A. Di Carlo, D.W.E. Allsopp, J. Zúñiga-Pérez, J. Appl. Phys. 2013, 114, 084307.

- [15] C.-C. Tsai, G.-H. Li, Y.-T. Lin, C.-W. Chang, P. Wadekar, Q.Y.-S. Chen, L. Rigutti, M. Tchernycheva, F.H. Julien, L.-W. Tu, Nanoscale Res. Lett. 2011, 6, 631.

- [16] S. Tanaka, Y. Kawaguchi, N. Sawaki, M. Hibino, K. Hiramatsu, Appl. Phys. Lett. 2000, 76, 2701.

- [17] A. Tanaka, W. Choi, R. Chen, S.A. Dayeh, Adv. Mater. 2017, 29, 1702557.

- [18] S. Dassonneville, A. Amokrane, B. Sieber, J.-L. Farvacque, B. Beaumont, P. Gibart, J. Appl. Phys. 2001, 89 3736.

- [19] O.-H. Nam, T.S. Zheleva, M.D. Bremser, R.F. Davis, J. Electron. Mater. 1998, 27 233–237.

- [20] T.S. Zheleva, S.A. Smith, D.B. Thomson, K.J. Linthicum, P. Rajagopal, R.F. Davis, J. Electron. Mater. 1999, 28, L5–L8.

- [21] U.T. Schwarz, P.J. Schuck, M.D. Mason, R.D. Grober, A.M. Roskowski, S. Einfeldt, R.F. Davis, Phys. Rev. B. 2003, 67, 045321.

- [22] M. S. Wong, S. Nakamura, S. P. DenBaars, ECS J. Solid State Sci. Technol. 2020, 9, 015012.

- [23] K. Baril, P. M. Coulon, M. Mrad, N. Labchir, G. Feuillet, M. Charles, B. Alloing, J. Appl. Phys. 2023, 133, 245702.

- [24] M. Mrad, K. Baril, M. Charles, J. Z. Perez, S. Labau, M. Panabiere, C. Gourgon, Micro Nano Eng. 2022, 14, 100110.

- [25] R. Dagher, P. de Mierry, B. Alloing, V. Brändli, B. Damilano, N. Mante, G. Feuillet, J. Cryst. Growth. 2019, 526, 125235.

- [26] M. Khoury, H. Li, B. Bonef, T. Mates, F. Wu, P. Li, S. P. DenBaars, Opt. Express, 2020, 28, 18150-18159.

- [27] M. Wehbe, M. Charles, K. Baril, B. Alloing, D. Pino Munoz, N. Labchir, P. Gergaud, J. Appl. Crystallography. 2023, 56, 643-649.

- [28] H. Lu, W. Guo, C. Su, X. Li, Y. Lu, Z. Chen, L. Zhu, IEEE ELECTRON. DEV. Soc. 2020, 8, 554-558.

- [29]Z. Pan, C. Guo, X. Wang, J. Liu, R. Cao, Y. Gong, Z. Gong, Adv. Mater. Tech. 2020, 5, 2000549.

- [30]K. S. Choi, J. Joo, Y. S. Eom, G. M. Choi, K. S. Jang, C. Lee, J. W. Choi, IEEE 71st Electronic Components and Technology Conference (ECTC). 2021, 1607-1613