## Special Session: On-chip jitter BIST with sub-picosecond resolution at GHz frequencies

Manasa Madhvaraj, Salvador Mir, Manuel J Barragan

### ▶ To cite this version:

Manasa Madhvaraj, Salvador Mir, Manuel J Barragan. Special Session: On-chip jitter BIST with sub-picosecond resolution at GHz frequencies. 2023 IEEE 24th Latin American Test Symposium (LATS), Mar 2023, Veracruz, Mexico. pp.1-2, 10.1109/lats58125.2023.10154493. hal-04253278

## HAL Id: hal-04253278 https://hal.univ-grenoble-alpes.fr/hal-04253278v1

Submitted on 24 Oct 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Special Session: On-chip jitter BIST with sub-picosecond resolution at GHz frequencies

Manasa Madhvaraj, Salvador Mir and Manuel J. Barragan Univ. Grenoble Alpes, CNRS, Grenoble INP\*, TIMA, F-38000 Grenoble, France

*Abstract*—This paper describes an on-chip instrument for jitter estimation of clock signals in the GHz range with a sub-picosecond resolution. A self-referenced technique is used to remove the need of a very clean external reference clock. The instrument has been designed in STMicroelectronics 28 nm FDSOI technology. By exploiting the fine delay control which can be achieved with this technology, simulation results haven shown a resolution down to 100 fs for GHz clock signals with a simple calibration procedure.

#### I. INTRODUCTION

Clock jitter is the deviation of a clock edge relative to a reference time frame. In the current age of high speed communication and I/O systems, clock jitter impacts the system performance. With increased data transfer rates, measuring clock jitter in the sub-picosecond range is becoming necessary. Jitter measurement with this level of resolution during production testing or through prototyping design stages needs high-speed oscilloscopes or spectrum analyzers which are also often expensive. On-chip jitter measurement offers a low-cost solution that also overcomes the inaccuracies in measurement that arise due to RLC effects while tapping high speed clocks for off-chip measurement.

On-chip jitter measurement techniques can be classified into two main categories that include, on one hand, the use of an external clock reference and, on the other hand, self-referenced techniques. The first category includes conventional techniques that use a clean reference and are often based on coherently undersampling the Signal Under Test (SUT) with the external clock.

Jitter estimation techniques that remove the need of an external reference clock are the second category of on-chip instruments and are generally termed as self-referenced techniques. These measurement schemes use a delayed version of the SUT to sample the clock itself to extract the jitter [1]. Self-referenced techniques for on-chip jitter measurement have been experimentally demonstrated with a resolution of 400 fs in [2], and 300 fs later in [3], for signals up to a few GHz. A resolution below 100 fs has been shown experimentally in [4], but with signals below 1 GHz with the use of a time-difference amplifier.

A self-referenced technique for random jitter estimation uses delay lines to sample the clock under test with a delayed version of itself at various instants of time in the vicinity of the expected clock edge. The probability that a given edge leads or lags its delayed version gives rise to a jitter histogram from which RMS jitter is computed [1]. This work proposes an implementation of a jitter test instrument using self-referenced technique in 28 nm FDSOI using the fine delay control achievable with this technology and demonstrates the feasibility of sub-picosecond resolution for clock jitter measurement in the GHz range.

#### II. A SELF-REFERENCED JITTER BIST

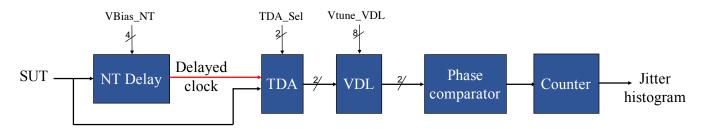

Fig. 1 shows the block diagram of the jitter test instrument using the self-referenced technique. This instrument has first an NT delay block to delay the SUT. This block is composed of a cascade of delay elements of the type described in [5] where N is the number of delayed periods and T the period of the SUT. The NT delayed clock acts as the sampling clock for the SUT. As demonstrated in [4], by setting the NT delay to multiples of the clock period, the jitter correlation between both signals will be very low (at least for random jitter) and the absolute jitter of the SUT can be extracted with a gain of  $\sqrt{2}$  from the N-period jitter that is measured by construction.

The Time Difference Amplifier (TDA) amplifies the time difference between the SUT and the sampling clock, thereby expanding the resolution of measurement by its gain. The SUT and sampling clock next traverse a Vernier Delay Line (VDL) made of a cascade of Vernier delay cells, each biased for a delay  $Gain_{TDA} \times \Delta$ , where  $\Delta$  is the target jitter resolution of 100 fs and the TDA gain is approximately 100. The Vernier delay cells are made of the same type of delay elements as for the NT delay. The sampling clock is incrementally delayed after each Vernier delay cell in the line. A phase comparator is used at the output of each VDL cell to detect the lead or lag of the SUT with respect to its delayed version. A counter stores the number of hits at the output of each VDL cell and this is used to generate the histogram.

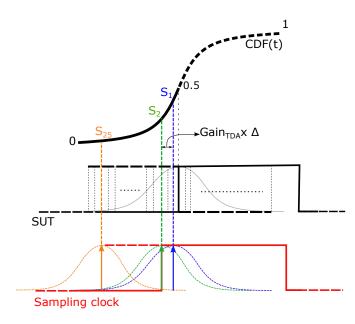

The principle for the generation of the jitter histogram is illustrated in Fig. 2 for a VDL that contains 25 delay cells. The outputs of each VDL cell allow computing one point of the Cumulative Distribution Function (CDF) of the jitter, at regular delays in the vicinity of the expected clock edge of the SUT. For each delay cell, the SUT is processed for a fixed timelength in order to produce the value of the corresponding CDF bin that is scanned out from the chip. The calculated bin values are assembled to produce the CDF. The jitter PDF is obtained off-chip by derivation of the CDF, and the absolute RMS jitter is calculated from it after correction by a factor of  $\sqrt{2}$ . It must be noticed that the implementation only considers sampling

<sup>\*</sup>Institute of Engineering Univ. Grenoble Alpes

Fig. 1. A self-referenced jitter BIST

Fig. 2. Generation of jitter CDF

one side of the SUT random jitter PDF that is considered symmetrical.

#### **III. SIMULATION RESULTS**

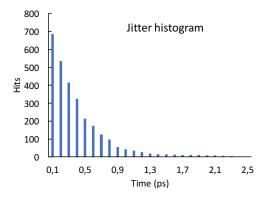

Simulation results have been obtained with a transistor level transient noise simulation of the instrument described in Fig. 1 with the counter and digital control circuitry modeled at higher level in Verilog-A. These Spectre simulations are extremely time consuming and often require few weeks of run time and implementing the digital circuitry that supports the programmability of the instrument in Verilog-A saves run time. The jitter histogram generated with a SUT frequency of 1 GHz is shown in Fig. 3. The vertical axis shows the number of hits for each of the bins in the histogram. These hits were obtained by simulating each bin for 1500 clock cycles. An RMS random jitter of 0.8 ps has been injected in the input clock signal. Post-processing of the obtained jitter histogram results in an measured RMS jitter estimate of 0.7 ps which shows a resolution of 100 fs.

#### **IV. CONCLUSIONS**

This paper has presented an implementation of an onchip jitter BIST in 28 nm FDSOI with simulation results

Fig. 3. Jitter histogram for 1 GHz clock frequency

that demonstrate the feasibility of a sub-picosecond resolution for jitter estimation for clocks up to 1 GHz. The FDSOI technology provides advantages due to tunability and low noise to reach a high resolution with simple calibration as described in [6]. A highly tunable delay element along with a TDA supports a sub-picosecond resolution of clock jitter measurement for frequencies in the GHz range.

#### **ACKNOWLEDGEMENTS**

This work has been carried out in collaboration with STMicroelectronics within the Nano2022 research program.

#### REFERENCES

- J.-J. Huang and J.-L. Huang, "A low-cost jitter measurement technique for BIST applications," *IEEE 12th Asian Test Symposium (ATS)*, pp. 336– 339, Nov. 2003.

- [2] K. Jenkins, A. P. Jose, and D. F. Heidel, "An on-chip jitter measurement circuit with sub-picosecond resolution," *31st European Solid-State Circuits Conference (ESSCIRC)*, pp. 157–160, Sept. 2005.

- [3] E. Gantsog, D. Liu, and A. B. Apsel, "0.89 mW on-chip jittermeasurement circuit for high speed clock with sub-picosecond resolution," *European Solid-State Circuits Conference*, pp. 457–460, 2016.

- [4] K. Niitsu, M. Sakurai, N. Harigai, T. J. Yamaguchi, and H. Kobayashi, "CMOS circuits to measure timing jitter using a self-referenced clock and a cascaded time difference amplifier with duty-cycle compensation," *IEEE Journal of Solid-State Circuits*, vol. 47, no. 11, pp. 2701–2710, Nov. 2012.

- [5] I. Sourikopoulos, A. Frappé, A. Cathelin, L. Clavier, and A. Kaiser, "A digital delay line with coarse/fine tuning through gate/body biasing in 28nm FDSOI," in ESSCIRC Conference 2016: 42nd European Solid-State Circuits Conference, 2016, pp. 145–148.

- [6] M. Madhvaraj, S. Mir, and M. J. Barragan, "A self-referenced on-chip jitter BIST with sub-picosecond resolution in 28 nm FD-SOI technology," in 2022 IFIP/IEEE 30th International Conference on Very Large Scale Integration (VLSI-SoC), 2022, pp. 1–6.