# Channel-Width-Dependent Mobility Degradation in Bulk Conduction Regime of Tri-Gate Junctionless Transistors

Dae-Young Jeon, Mireille Mouis, Sylvain Barraud, Gerard Ghibaudo

## ▶ To cite this version:

Dae-Young Jeon, Mireille Mouis, Sylvain Barraud, Gerard Ghibaudo. Channel-Width-Dependent Mobility Degradation in Bulk Conduction Regime of Tri-Gate Junctionless Transistors. IEEE Transactions on Electron Devices, 2022, 69 (6), pp.3037-3041. 10.1109/TED.2022.3172056. hal-03697387

# HAL Id: hal-03697387 https://hal.univ-grenoble-alpes.fr/hal-03697387

Submitted on 29 Aug 2022

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Channel-width dependent mobility degradation in bulk conduction regime of tri-gate junctionless transistors

Dae-Young Jeon, Mireille Mouis, Senior Member, IEEE, Sylvain Barraud and Gérard Ghibaudo. Fellow, IEEE

Abstract—Junctionless transistors (JLTs) have promising strengths such as extremely simple structures without p-n junctions, better reliability and low flicker noise, for overcoming scaling challenges for advanced sub-5nm nodes. In this paper, channel-width dependent operation in partially depleted regime of tri-gate JLTs were investigated with comparison to conduction conventional inversion-mode (IM) transistors. A large transconductance difference of  $(g_m)$ against gate-to-channel capacitance (Cgc), and the reduced amplitude of first peak on dg<sub>m</sub>/dV<sub>g</sub> were identified under the partially depleted regime in JLTs, due to a severe transverse E-field near threshold voltage (Vth). However, the impact of E-field was weakened as decreasing channel-width of JLTs. These works provide a key information for better understanding channel-width dependent performance of JLTs and for implementing practical applications with them.

Index Terms—Channel-width dependence, nanowire (NW)-like structure, partially depleted regime, peaks on  $dg_m/dV_g$ , tri-gate junctionless transistors (JLTs), transconductance ( $g_m$ ) degradation, transverse electric-field (E-field).

### I. INTRODUCTION

FURTHER scaling down of transistors is continuously required in the fourth industrial revolution era, explained by Internet of Things (IoT), artificial intelligence (AI), mobile devices and big data with cloud computing [1]. A number of efforts, in terms of gate stack, strain engineering, 3-dimensional structures and alternative channel materials, have been suggested to fulfill power, performance, area and cost with minimizing short channel effects (SCEs) [2-5]. Recently, junctionless transistors (JLTs) have received considerable attention to overcome scaling challenges for advanced sub-5nm nodes. Extremely simple structures without p-n-junctions,

This work was supported by European Union 7th Framework Program project SQWIRE under grant agreements No. 257111 and the National Research Foundation of Korea (NRF-2017M3A7B4049167).

better reliability and lower flicker noise are key advantages of JLTs [7-15]. An additional implantation process on source and drain regions can also improve performance of JLTs with reducing access resistance [16]. In addition, advanced transistors with excellent short-channel characteristics, high-performance sensors and multifunctional devices have been implemented as JLTs with a variety of materials, including polycrystalline silicon (Si), III–V semiconductors, and 2-D transition metal dichalcogenides (TMDs) [7].

In this paper, the channel-width influenced operation in partially depleted regime of JLTs were investigated in detail. Behavior of bulk conduction near threshold voltage ( $V_{th}$ ) of planar-like JLTs was more affected by transverse electric-field (E-field), than conduction in conventional inversion-mode (IM) transistors. However, the impact of E-field near  $V_{th}$  was mitigated in nanowire (NW)-like JLTs due to effects of sidewall gates. Consistent results were also shown in temperature dependence of electrical properties in JLTs and numerical simulation works.

### II. EXPERIMENTS

JLTs were fabricated at CEA-Leti on (100) SOI wafers with device  $Si \approx 9.2$  nm, high-k dielectric  $\approx 1.2$  nm and thick buried oxide (BOX)  $\approx$  145 nm. JLT channel was highly doped with phosphorus targeted at 10<sup>19</sup>/cm<sup>3</sup>, and IM transistors were also fabricated by the same process only except for channel doping concentration. Further detail processes for device fabrication and material parameters were explained in previous works [17,18].Current-voltage characteristics with temperatures from 80 K to 350 K were measured by using HP 4155A semiconductor parameter analyzer, and HP4294a with a 50 mV small signal at 500 kHz was used for getting capacitance-voltage characteristics. In case of gate-to-channel capacitance (Cgc) measurements of NW-like JLTs, devices with very long gate-length (L =  $10 \mu m$ ) were selected in arrays of 50channels, for a better accuracy with minimizing contact resistance effect and mobility degradation induced by drain-bias. In addition, FlexPDE software based on finite element models was used for obtaining simulated results.

### III. DISCUSSION

Figure 1(a) and 1(b) show gate-to-channel capacitance ( $C_{\rm gc}$ ), its derivative ( $dC_{\rm gc}/dV_{\rm g}$ ), corresponding transconductance ( $g_{\rm m}$ ) and  $dg_{\rm m}/dV_{\rm g}$  of a planar-like IM transistor with a long

D.-Y. Jeon is with Institute of Advanced Composite Materials, Korea Institute of Science and Technology, Joellabuk-do 55324, South Korea (e-mail: dyjeon@kist.re.kr).

M. Mouis and G. Ghibaudo are with IMEP-LAHC, Grenoble INP, Minatec, BP 257, 38016 Grenoble, France.

S. Barraud is with CEA-LETI Minatec, 17 rue des Martyrs, 38054 Grenoble, France.

gate-length (L = 10  $\mu$ m), respectively. The  $C_{gc}$  and  $dC_{gc}/dV_g$  characteristics are theoretically equivalent to  $g_m$  and  $dg_m/dV_g$  ones, except that there are no mobility degradation effects, mainly resulting from transverse E-field, nor series resistance effects in the capacitance-based characteristics [19].

Fig. 1. (a) Measured  $C_{gc},\,g_m,\,(b)\,dC_{gc}/dV_g$  and  $dg_m/dV_g$  of a planar-like IM transistor (L = W = 10  $\mu m)$  as illustrated in Fig. 1(a). (c) Measured  $C_{gc},\,g_m,\,(d)\,dC_{gc}/dV_g$  and  $dg_m/dV_g$  of a planar-like JLT (L = W = 10  $\mu m)$  as illustrated in Fig. 1(c). The devices were biased in the linear operation regime with  $V_d$  = 20 mV at T = 300 K.

As  $V_g$  was increased,  $C_{gc}$  in the red curve of Fig. 1(a) started to increase as a result of the formation of inversion channel, then reached a maximum value, which denotes capacitance of gate-insulator. The dCgc/dVg plot in Fig. 1(b) also showed a single peak meaning threshold voltage ( $V_{th} \approx 0.4 \text{ V}$ ). The behavior of g<sub>m</sub> and dg<sub>m</sub>/dV<sub>g</sub> near V<sub>th</sub> was very consistent to that of Cgc and dCgc/dVg, while a significant degradation of gm was observed for further increasing  $V_g$  (> 0.75 V) due to surface roughness scattering [20]. In addition, the C<sub>gc</sub>, dC<sub>gc</sub>/dV<sub>g</sub>, g<sub>m</sub> and dg<sub>m</sub>/dV<sub>g</sub> curves of a planar-like JLT with the same geometry were plotted in Fig. 1(c) and 1(d). A shoulder shape on  $C_{gc}$  and two clear peaks on dCgc/dVg, positioned at threshold voltage  $(V_{th})$  and at flat-band voltage  $(V_{fb})$ , were clearly observed. They are typical of JLTs, as a manifestation of bulk channel conduction [7,18]. Compared with IM devices, less g<sub>m</sub> degradation at large V<sub>g</sub> (> 0.75 V) was observed in Fig. 1(c) consistently with previous results [21,22]. However, near  $V_{th}$ , the C<sub>gc</sub> and g<sub>m</sub> plots of the JLT were displaying very different behaviors. In particular, g<sub>m</sub> displayed a much smaller shoulder than  $C_{gc}$  and the two peaks observed on  $dC_{gc}/dV_g$  and  $dg_m/dV_g$ characteristics displayed inverse relative amplitudes. Such discrepancies could be due to a non-uniform distribution of point defects in the JLT channel [23], and a severe transverse E-field during operation near  $V_g = V_{th}$ .

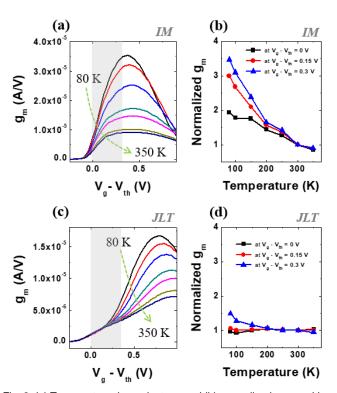

Temperature dependent  $g_m$  of the planar-like IM transistor was plotted as a function of gate voltage overdrive ( $V_g - V_{th}$ ) as shown in Fig. 2 (a).  $V_{th}$  with varying temperature was determined by using the constant current technique at  $I_d \times L/W \approx 10^{-7}$  A. It is well known as  $g_m$  is strongly related to the trend of effective mobility ( $\mu_{eff}$ ), and temperature dependent  $\mu_{eff}$  can be given by an empirical mobility model based on Matthiessen's rule as [24,25]:

$$\frac{1}{\mu_{eff}(T)} = \frac{1}{\frac{300}{T} \times ph} + \frac{1}{\frac{T}{300} \times C} + \frac{1}{neu} + \frac{1}{sr}$$

(1)

where ph, C, neu and sr denote  $\mu_{eff}$ -contributions resulted from phonon scattering, Coulomb scattering, neutral defect scattering and surface roughness scattering, respectively. Normalized g<sub>m</sub> near V<sub>th</sub> in Fig. 2(b) tended to increase as decreasing temperature, indicating acoustic phonon-dominated scattering. Figure 2(c) showed temperature dependence of g<sub>m</sub> in the planar-like JLT. A typical phonon scattering governed behavior was identified for the regime of  $V_g - V_{th} > 0.5 \text{ V}$ . However, the value of  $g_m$  near  $V_{th}$  seemed not to change about the temperature variation. Indeed, the normalized g<sub>m</sub> in Fig. 2(d) was slightly changed only by varying temperature due to temperature independent surface roughness (SR) scattering as well as defect-induced scattering [26,27]. A SR-like scattering of charge carriers can be induced between bulk neutral channel and depletion area in JLT by a considerable transverse E-field in the partially depleted operation-regime.

Fig. 2. (a) Temperature dependent  $g_m$ , and (b) normalized  $g_m$  near  $V_{th}$  as marked in gray of Fig. 2(a) versus temperature of planar-like IM transistor. (c) Temperature dependent  $g_m$ , and (d) normalized  $g_m$  near

$V_{th}$  as marked in gray of Fig. 2(c) versus temperature of planar-like JLT. The devices were biased in the linear operation regime with  $V_d$  = 20 mV.

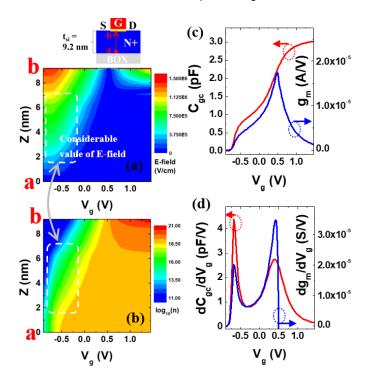

Fig. 3. (a) Simulated distribution of transverse E-field and (b) charge carrier concentration (n), across the JLT channel (from bottom interface 'a' to top interface 'b' in the illustration). The ordinate z refers to the distance from bottom Si/BOX interface. The evolution of these distributions is shown as a function of V<sub>g</sub>, in abscissa. (c) Corresponding plots of  $C_{\rm gc},\,g_{\rm m},\,$  (d)  $dC_{\rm gc}/dV_{\rm g}$  and  $dg_{\rm m}/dV_{\rm g}.$

The variation of transverse electric field (E-field) and charge carrier concentration (n), along the cutline a-b which goes from bottom to top interface across the JLT channel, is mapped against V<sub>g</sub> in Fig. 3(a) and 3(b), respectively [12]. Depending on V<sub>g</sub>, there are two conduction regimes in JLTs, with bulk conduction for  $V_{th} < V_g < V_{fb}$  and surface accumulation for  $V_g >$ V<sub>fb</sub>. Transverse E-field at the interface between Si channel and gate-insulator is getting reduced as decreasing V<sub>g</sub>, and then, the magnitude of the E-field is theoretically zero when Vg reaches  $V_{\text{fb}}$ . Moreover, for further decreasing  $V_{\text{g}}$ , the E-field is reinforced again in the partial depletion-state of JLT [21,23]. For  $V_g = V_{fb}$  ( $\approx 0.5 \text{ V}$ ), effectively zero E-field throughout the JLT channel was verified in blue as shown in Fig. 3(a), and whole JLT channel is full of charge carriers with  $log_{10}(n) = 19$ in orange color in Fig. 3(b). As decreasing  $V_g < V_{fb}$ , the value of E-field is getting increased from the top interface, and these give rise to the depletion of charge carriers. Therefore, degradation of bulk channel mobility in the partially depleted regime of JLT can occur, since electron charge carriers at V<sub>th</sub> <  $V_{\rm g} < V_{\rm fb}$  are influenced by considerable value of E-field as indicated in the white dotted line of Fig. 3(a) and 3(b). Corresponding C<sub>gc</sub>, dC<sub>gc</sub>/dV<sub>g</sub>, g<sub>m</sub> and dg<sub>m</sub>/dV<sub>g</sub> were plotted in Fig. 3(c) and 3(d). The  $g_m$  was simulated with considering a transverse E-field affected mobility ( $\mu_{field}$ ) as [28]:

$$\mu_{field} = \frac{\mu_0}{1 + \left(\frac{E_{eff}}{E}\right)^{\alpha}}$$

(2)

where  $\mu_0$ ,  $E_{eff}$ ,  $E_c$  and  $\alpha$  denote low-field mobility (= 150 cm<sup>2</sup>/Vs), effective transverse E-field, critical E-field (=  $5 \times 10^5$  V/cm) and the mobility attenuation exponent (= 1.5), respectively. Mobility degradation with respect to non-uniform defects in the channel was also taken into account with following equation [29]:

$$\mu_0 = \mu_{back0} + (\mu_{top0} - \mu_{back0}) \times \frac{y}{t_{si}}, \quad [0 \le y \le t_{si}] \quad (3)$$

where  $\mu_{top0}$  and  $\mu_{back0}$  are low-field mobility at top interface (= 150 cm²/Vs) and bottom interface (= 100 cm²/Vs), individually. Similar behavior to the experimental results in Fig. 1(c), such as clearly reduced shoulder shape, was investigated in Fig. 3(c). Trend of relative amplitude-ratio between first and second peak on  $dC_{gc}/dV_g$  and  $dg_m/dV_g$  in Fig. 3(d) was also consistent to that in Fig. 1(d).

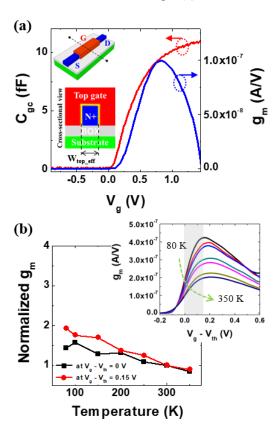

Fig. 4. (a) Measured  $C_{gc}$  and  $g_m$  of a NW-like JLT ( $W_{top\_eff} \approx 25$  nm, L = 10 µm), as described in the illustration (T = 300 K). (b) Normalized  $g_m$  near  $V_{th}$  as marked in gray of the inset versus temperature of the NW-like JLT. The device was biased in the linear operation regime with  $V_d = 50$  mV

Figure 4(a) shows the measured  $C_{gc}$  and  $g_m$  of a NW-like JLT with top-effective width  $(W_{top\_eff}) \approx 25$  nm. Shoulder shape near  $V_{th}$  was vanished due to the shrunk portion of bulk neutral channel as compared to surface accumulation channel, and

enhanced sidewall gate effects [30]. In addition, difference between  $C_{gc}$  and  $g_m$  for 0 V <  $V_g$  < 0.5 V (the partial depletion-state) has significantly narrowed as compared to the results from the planar-like JLT in Fig. 1(c). Normalized  $g_m$  near  $V_{th}$  was also increased as decreasing temperature in Fig. 4(b). One can expect that SR scattering is reduced and then, impact of phonon scattering is relatively getting stronger in the operating regime of NW-like JLT.

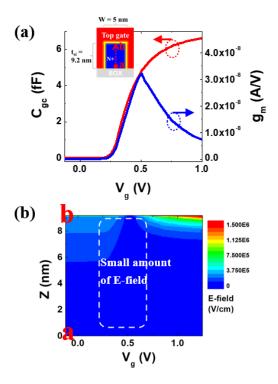

Fig. 5. (a) Simulated  $C_{gc}$  and  $g_m$  of a NW-like JLT (W = 5 nm, L = 10  $\mu m$  and  $V_d$  = 50 mV). (b) Corresponding distribution of transverse E-field, across the NW-like JLT channel from bottom interface 'a' to top interface 'b' in the illustration of Fig. 5(a). The ordinate z refers to the distance from bottom Si/BOX interface.

Simulated  $C_{gc}$  and  $g_m$  of a NW-like JLT with W = 5 nm and L = 10 µm were plotted in Fig. 5(a). Corresponding distribution of transverse E-field was also shown in Fig. 5(b) [30]. Indeed, only a slight variation between  $C_{gc}$  and  $g_m$  shape was observed for 0.25 V <  $V_g$  < 0.5 V, and magnitude of transverse E-field was negligible in that operating regime, as identified in the white dotted line of Fig. 5(b). Sidewall gate effects in the NW structures cause the weakened SR scattering in the partially depleted operation. Furthermore, as the width of tri-gate JLTs decreases,  $V_{th}$  position is getting closer to  $V_{tb}$  [30,31]. Even from this point of view, the reduced E-field effects and less degradation of  $g_m$  near  $V_{th}$  in the NW-like JLTs is quite reasonable.

### IV. CONCLUSION

Channel-width dependent behavior of bulk conduction in JLTs were investigated for the first time. Even though less transconductance (g<sub>m</sub>) degradation for a strong accumulation-operation in JLTs was observed as compared to

that of inversion-mode (IM) transistors, the reduced amplitude of first peak on  $dg_m/dV_g$ , and a large variation between  $C_{gc}$  and  $g_m$  near  $V_{th}$  operation-regime were shown in JLTs, since a severe transverse E-field under the partially depleted operation. However, weakened E-field effects and less degradation of  $g_m$  near  $V_{th}$  were identified in nanowire (NW)-like JLTs, due to impact of sidewall gates in the narrow structures. Those results were also verified by temperature dependence of  $g_m$  behavior, and numerical simulation about distribution of transverse E-field and charge carrier concentration in JLT channel. In addition, a significant  $V_{th}$  variation with changing width of tri-gate JLTs [30,31] can be explained well by the results.

### REFERENCES

- [1] M. Badaroglu, "IEEE international roadmap for devices and systems," More Moore, White Paper, 2021. [Online] Available: https://irds.ieee.org/roadmap-2021.

- [2] A. Veloso et al., "Gate-all-around NWFETs vs. triple-gate FinFETs: Junctionless vs. extensionless and conventional junction devices with controlled EWF modulation for multi-VT CMOS," in 2015 Symposium on VLSI Technology (VLSI Technology), 2015, pp. T138-T139: IEEE. doi: 10.1109/VLSIT.2015.7223652.

- [3] A. Veloso et al., "Junctionless versus inversion-mode lateral semiconductor nanowire transistors," Journal of Physics: Condensed Matter, vol. 30, no. 38, p. 384002, 2018. doi: 10.1088/1361-648X/aad7c7.

- [4] N. G. Orji et al., "Metrology for the next generation of semiconductor devices," Nature electronics, vol. 1, no. 10, pp. 532-547, 2018. doi: 10.1038/s41928-018-0150-9.

- [5] S. Salahuddin, K. Ni, and S. Datta, "The era of hyper-scaling in electronics," Nature electronics, vol. 1, no. 8, pp. 442-450, 2018. doi: 10.1038/s41928-018-0117-x.

- [6] J.-P. Colinge et al., "Nanowire transistors without junctions," Nature nanotechnology, vol. 5, no. 3, pp. 225-229, 2010. doi: 10.1038/nnano.2010.15.

- [7] S. Deleonibus, Emerging Devices for Low-power and High-performance Nanosystems: Physics, Novel Functions, and Data Processing. CRC Press, 2018. doi: 10.1201/9780429458736.

- [8] T. A. Oproglidis et al., "Impact of Hot Carrier Aging on the 1/f and Random Telegraph Noise of Short-Channel Triple-Gate Junctionless MOSFETs," IEEE Transactions on Device and Materials Reliability, vol. 21, no. 3, pp. 348-353, 2021. doi: 10.1109/TDMR.2021.3094510.

- [9] W. C.-Y. Ma and C.-J. Tsai, "Impacts of Independent Dual-Gate Operation on Reliability of Nanosheet Junctionless Thin-Film Transistor," IEEE Transactions on Electron Devices, vol. 68, no. 12, pp. 6171-6176, 2021. doi: 10.1109/TED.2021.3117901.

- [10] Y.-R. Lin et al., "Performance of Junctionless and inversion-mode thin-film transistors with stacked Nanosheet channels," IEEE Transactions on Nanotechnology, vol. 19, pp. 84-88, 2019. doi: 10.1109/TNANO.2019.2960836.

- [11] D.-R. Hsieh, K.-C. Lin, C.-C. Lee, and T.-S. Chao, "Reliability of p-Type Pi-Gate Poly-Si Nanowire Channel Junctionless Accumulation-Mode FETs," IEEE Transactions on Electron Devices, vol. 68, no. 6, pp. 2647-2652, 2021. doi: 10.1109/TED.2021.3075665.

- [12] D.-Y. Jeon, "Channel geometry-dependent threshold voltage and transconductance degradation in gate-all-around nanosheet junctionless transistors," AIP Advances, vol. 11, no. 5, p. 055111, 2021. doi: 10.1063/5.0035460.

- [13] D.-Y. Jeon, "Simple estimation of intrinsic electrical parameters in junctionless transistors," AIP Advances, vol. 10, no. 9, p. 095118, 2020. doi: 10.1063/5.0022769.

- [14] D.-Y. Jeon, S. J. Park, M. Mouis, S. Barraud, G.-T. Kim, and G. Ghibaudo, "Impact of series resistance on the operation of junctionless transistors," Solid-State Electronics, vol. 129, pp. 103-107, 2017. doi: 10.1016/j.sse.2016.12.004.

- [15] D.-Y. Jeon, S. J. Park, M. Mouis, S. Barraud, G.-T. Kim, and G. Ghibaudo, "New method for the extraction of bulk channel mobility and flat-band voltage in junctionless transistors," Solid-State Electronics, vol. 89, pp. 139-141, 2013. doi: 10.1016/j.sse.2013.08.003.

- [16] C.-W. Lee et al., "Performance estimation of junctionless multigate transistors," Solid-State Electronics, vol. 54, no. 2, pp. 97-103, 2010. doi.org/10.1016/j.sse.2009.12.003

- [17] D.-Y. Jeon, S. J. Park, M. Mouis, S. Barraud, G.-T. Kim, and G. Ghibaudo, "Low-temperature electrical characterization of junctionless transistors," Solid-State Electronics, vol. 80, pp. 135-141, 2013. doi: 10.1016/j.sse.2012.10.018.

- [18] D.-Y. Jeon et al., "Revisited parameter extraction methodology for electrical characterization of junctionless transistors," Solid-State Electronics, vol. 90, pp. 86-93, 2013. doi: 10.1016/J.SSE.2013.02.047.

- [19] T. Rudenko, V. Kilchytska, J.-P. Raskin, A. Nazarov, and D. Flandre, "Special features of the back-gate effects in ultra-thin body SOI MOSFETs," in Semiconductor-On-Insulator Materials for Nanoelectronics Applications: Springer, 2011, pp. 323-339. doi: 10.1007/978-3-642-15868-1\_18.

- [20] G. Ghibaudo, "Critical MOSFETs operation for low voltage/low power IC's: Ideal characteristics, parameter extraction, electrical noise and RTS fluctuations," Microelectronic engineering, vol. 39, no. 1-4, pp. 31-57, 1997. doi: 10.1016/S0167-9317(97)00166-4.

- [21] J.-P. Colinge et al., "Reduced electric field in junctionless transistors," Applied Physics Letters, vol. 96, no. 7, p. 073510, 2010. doi: 10.1063/1.3299014.

- [22] S. J. Park et al., "Less mobility degradation induced by transverse electric-field in junctionless transistors," Applied Physics Letters, vol. 105, no. 21, p. 213504, 2014. doi: 10.1063/1.4902549.

- [23] D.-Y. Jeon et al., "Separation of surface accumulation and bulk neutral channel in junctionless transistors," Applied Physics Letters, vol. 104, no. 26, p. 263510, 2014. doi: 10.1063/1.4886139.

- [24] B. Szelag and F. Balestra, "Transconductance enhancement at low temperatures in deep submicrometre MOSFETs," Electronics Letters, vol. 34, no. 18, pp. 1793-1794, 1998. doi: 10.1049/el:19981227.

- [25] D.-Y. Jeon, S. J. Park, M. Mouis, S. Barraud, G.-T. Kim, and G. Ghibaudo, "Low-temperature operation of junctionless nanowire transistors: Less surface roughness scattering effects and dominant scattering mechanisms," Applied Physics Letters, vol. 105, no. 26, p. 263505, 2014. doi: 10.1063/1.4905366.

- [26] D. S. Jeon and D. E. Burk, "MOSFET electron inversion layer mobilities-a physically based semi-empirical model for a wide temperature range," IEEE Transactions on Electron Devices, vol. 36, pp. 1456-1463, 1989. doi: 10.1109/16.30959.

- [27] S.-i. Takagi, A. Toriumi, M. Iwase, and H. Tango, "On the universality of inversion layer mobility in Si MOSFET's: Part I-effects of substrate impurity concentration," IEEE Transactions on Electron Devices, vol. 41, no. 12, pp. 2357-2362, 1994. doi: 10.1109/16.337449.

- [28] M.-S. Liang, J. Y. Choi, P.-K. Ko, and C. Hu, "Inversion-layer capacitance and mobility of very thin gate-oxide MOSFET's," IEEE Transactions on Electron Devices, vol. 33, no. 3, pp. 409-413, 1986. doi: 10.1109/T-ED.1986.22502.

- [29] S. J. Park, D.-Y. Jeon, L. Montes, S. Barraud, G.-T. Kim, and G. Ghibaudo, "Impact of channel width on back biasing effect in tri-gate MOSFET," Microelectronic engineering, vol. 114, pp. 91-97, 2014. doi: 10.1016/j.mee.2013.09.016.

- [30] D.-Y. Jeon, S. J. Park, M. Mouis, S. Barraud, G.-T. Kim, and G. Ghibaudo, "Effects of channel width variation on electrical characteristics of tri-gate Junctionless transistors," Solid-State Electronics, vol. 81, pp. 58-62, 2013. doi: 10.1016/j.sse.2013.01.002.

- [31] S.-J. Choi, D.-I. Moon, S. Kim, J. P. Duarte, and Y.-K. Choi, "Sensitivity of threshold voltage to nanowire width variation in junctionless transistors," IEEE Electron Device Letters, vol. 32, no. 2, pp. 125-127, 2010. doi: 10.1109/LED.2010.2093506.