## Probing impact on pad moisture tightness: A challenge for pad size reduction

Matthias Vidal-Dhô, Quentin Hubert, Patrice Gonon, Philippe Delorme, Jonathan Jacquot, Maxime Marchetti, Ludovic Beauvisage, Jean-Michel Moragues, Pascale Potard, Pascal Fornara, et al.

### ▶ To cite this version:

Matthias Vidal-Dhô, Quentin Hubert, Patrice Gonon, Philippe Delorme, Jonathan Jacquot, et al.. Probing impact on pad moisture tightness: A challenge for pad size reduction. Conference on Microelectronic Test Structures (ICMTS), 2019, Kita-Kyushu, Japan. pp.176-179, 10.1109/ICMTS.2019.8730990. hal-02362746

## HAL Id: hal-02362746 https://hal.univ-grenoble-alpes.fr/hal-02362746v1

Submitted on 28 Feb 2024  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Probing impact on pad moisture tightness: a challenge for pad size reduction

Matthias Vidal-Dhô<sup>1,2</sup>, Quentin Hubert<sup>1</sup>, Patrice Gonon<sup>2</sup>, Philippe Delorme<sup>1</sup>, Jonathan Jacquot<sup>1</sup>, Maxime Marchetti<sup>1</sup>, Ludovic Beauvisage<sup>1</sup>, Jean-Michel Moragues<sup>1</sup>, Pascale Potard<sup>1</sup>, Pascal Fornara<sup>1</sup>, Jean-Philippe Escales<sup>1</sup>, Pascal Sallagoity<sup>1</sup>, Olivier Pizzuto<sup>1</sup>, Delphine Maury<sup>1</sup>, Jean-Michel Mirabel<sup>1</sup>.

<sup>1</sup>STMicroelectronics Rousset, 190, avenue Célestin Coq, 13106 Rousset, France <sup>2</sup>LTM CNRS, 17, avenue des martyrs, 38054 Grenoble, France Email: matthias.vidaldho@st.com/quentin.hubert@st.com

*Abstract*— This paper underlines the damages induced by probing on narrow pads reliability of specifically designed test structures placed on dicing streets and indicates that probing during electrical test steps provokes detrimental cracks diving from the passivation through the BEOL layers providing a path for moisture ingress.

Keywords—pad, moisture, leakage, crack, reliability, size reduction, moisture ingress

#### I. INTRODUCTION

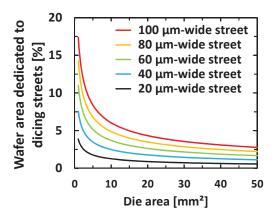

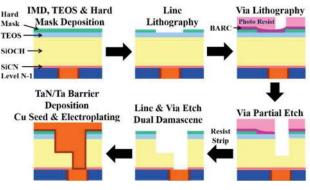

In many applications such as automotive and medical, chips must be highly reliable and thus, pass challenging quality assessments including Wafer-Level Reliability evaluation, exhaustive Parametric Test and extended Wafer Sort. To fulfill such demanding Electrical requirements, a large number of test structures - placed in wafer dicing streets - are needed. However, the smaller the die, the higher the wafer area dedicated to dicing streets (Figure 1). Therefore, a way to reduce the dicing streets area is to reduce the street width. To this extent, structures with narrower pads are mandatory. Probing equipment having a limited precision, hitting small pads in reduced street width might provoke non-previously existing reliability issues in test structures. In this paper, the impact of probing on narrow pads integrity of specifically designed test structures is evaluated with dedicated test methods. These test structures are embedded in an automotive-qualified 90nm-node of a 200mm process line with 3 dual-damascene copper-levels Back-End-Of-Line (BEOL) with SiCOH low-k intermetallic dielectric (IMD), 45 nm-thick SiCN capping layer and Ta/TaN diffusion barrier [1]. Figure 2 describes the process flow of one metal layer.

Figure 1: Percentage of wafer area dedicated to dicing streets as a function of die area. Percentages are calculated assuming a square die and same street width on X and Y. When the die is not a square, the percentage of wafer area dedicated to dicing streets might be slightly different.

Figure 2: Process flow used to fabricate one metal layer. To create successive metal layers, this sequence is repeated

#### II. TEST STRUCTIRES:

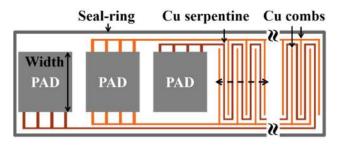

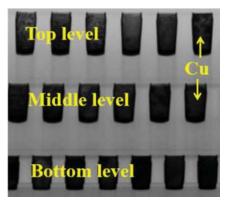

The elementary studied structure is composed of a metal serpentine running between two interwoven metal combs each one being connected to a dedicated pad used for biasing and sensing (Figure 3.a). This structure is replicated in the 3 metal layers connected to independent pads allowing to test each level independently (Figure 3.b). To ensure that pollutants and moisture will not contaminate the structure from the side, it is fully enclosed by a seal-ring [2]. Table I indicates drawn metal spacing, width and serpentine length. Devices with pad width varying from 30  $\mu$ m to 130  $\mu$ m with a step of 20  $\mu$ m have been designed. To remain compatible with 90nm probing equipment, pads spacing and height are kept to 60 $\mu$ m and 70 $\mu$ m, respectively.

Figure 3.a: Elementary studied structure composed of a metal serpentine running between two interwoven metal combs and surrounded by a seal-ring.

Figure 3.b: Cross-section TEM image of the test structure with the 3 metal levels. The cross-section location is indicated by the black dashed arrow on Figure 3.a.

TABLE 1: DRAWN TEST STRUCTURE DIMENSIONS FOR EVERY METAL LEVEL.

| Metal<br>level | Space<br>[nm] | Width<br>[nm] | Serpentine<br>length [cm] |

|----------------|---------------|---------------|---------------------------|

| Bottom         | 120           | 120           | 99                        |

| Middle         | 126           | 134           | 89                        |

| Тор            | 126           | 134           | 86                        |

III. EXPERIMENTS - RESULTS:

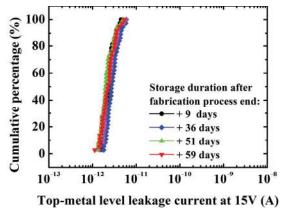

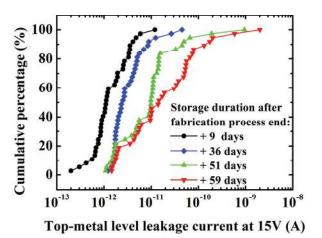

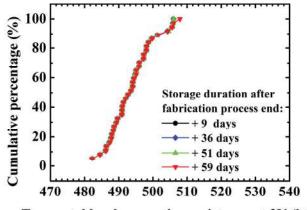

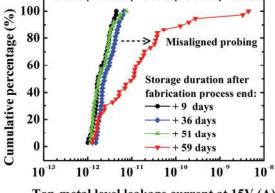

At the end of the fabrication process, structure leakage current has been regularly measured during 59 days with a bias of 15 V while wafers were stored at room condition. When the pad width is between 50 and 130  $\mu$ m, leakage does not evolve as time since fabrication process end increases (Figure 4). To the contrary, for 30 $\mu$ m-wide pad structures, the leakage increases dramatically right after the first measurement (Figure 5). In order to ensure that leakage current increase observed on 30 $\mu$ m-wide pads structure is not the consequence of copper corrosion, serpentine resistance measurements have been carried out. Figure 6 plots the 30  $\mu$ m-wide pads structure results that confirms the serpentine resistances does not evolve and thus there is no copper corrosion. Measurements for structures with wider pads produce similar distributions.

Figure 4: Top-metal level leakage current at 15 V of the structure with 70 $\mu$ m-wide pads measured after 9, 36, 51 and 59 days of storage at room condition after fabrication process end. Similar results are obtained on the two other metal levels and on structures with 90, 110 and 130 $\mu$ m-wide pads.

Figure 5: Top-metal level leakage current at 15 V of the structure with  $30\mu$ m-wide pads measured after 9, 36, 51 and 59 days of storage at room condition after fabrication process end. Similar results are obtained on the two other metal levels.

Top-metal level serpentine resistance at 2V (kΩ)

Figure 6: Top-metal level serpentine resistance at 2 V of the structure with  $30\mu$ m-wide pads measured after 9, 36, 51 and 59 days of storage at room condition after fabrication process end. Similar results are obtained on the two other metal levels.

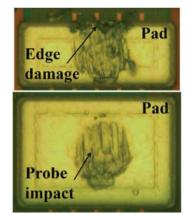

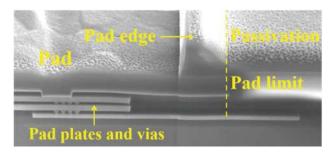

Every structure has been observed using an optical microscope and only 30  $\mu$ m-wide pad edges are found to be widely damaged (Figure 7). Hence, pads have been imaged using cross-section SEM. Before probing, no crack is seen in the BEOL layers indicating that, even with the 30 $\mu$ m-wide pad, there is no fabrication process issue (Figure 8).

Figure 7: Optical top-view of a widely damaged  $30 \mu m$ -wide pad (left) and a  $50 \mu m$ -wide pad (right).

Figure 8: Cross-section SEM image of a  $30\mu m$ -wide pad and pad edge before any probing. Neither cracks nor fabrication process issue is observed.

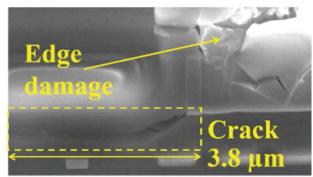

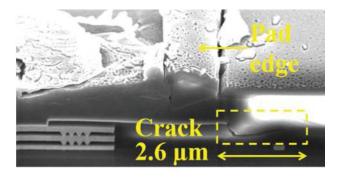

However, after probing, a detrimental crack diving from the top of the stack is observed (Figure 9). A well-known issue in SiOCH low-k material is their propensity to absorb moisture over time, degrading their key properties such as leakage current [2]. Therefore, we can assume that the observed leakage current increase is due to moisture ingress through the identified cracks. To confirm this assumption, a slightly misaligned probing has been performed on 50µmwide pads just after the measurement carried out 51 days after fabrication process end. On the measurement performed only 8 days later, a leakage current increase is observed on the 50µm-wide pads structure while no increase is seen for 70, 90, 110 and 130µm-wide pads structures (Figure 10). Crosssection SEM observations of damaged 50µm-wide pads from leaky structures reveal deep cracks diving from the pads edge to BEOL layers providing a path for moisture ingress (Figure 11).

Figure 9: Cross-section SEM image of a  $30\mu$ m-wide pad edge after probing. A deep crack diving from the top of the BEOL layers is observed and is more than  $4\mu$ m-long.

Top-metal level leakage current at 15V (A)

Figure 10: Top-metal level leakage current at 15 V of the structure with 50  $\mu$ m-wide pads measured after 9, 36, 51 and 59 days of storage at room condition after fabrication process end. Similar results are obtained on the two other metal levels.

Figure 11: Cross-section SEM image of a  $50\mu$ m-wide pad edge after misaligned probing. A deep crack diving from the top of the stack is observed and its length is 2.6  $\mu$ m.

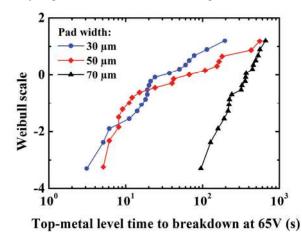

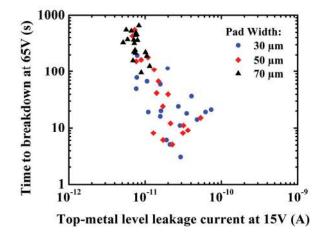

TDDB measurements have been carried out with a bias of 65 V and a clear degradation of both time-to-breakdown ( $T_{BD}$ ) median and spread is observed on structures with 30 and 50µm-wide pads i.e. on structures where cracks have been identified (Figure 12). The correlation between leakage current measured just before TDDB measurement and  $T_{BD}$  confirms the link between moisture ingress through cracks and reliability degradation of the structures (Figure 13).

Figure 12: Weibull distribution of the time-to-breakdown of the top-metal level structures with 30-, 50- and 70- $\mu$ m wide pads measured after 59 days of storage at room condition.

Figure 13: Time-to-breakdown of the top-metal level with 30, 50 and 70 $\mu$ m-wide pads after 59 days of storage as a function of leakage current measured just before TDDB measure. The lower the leakage current, the higher the time-to-breakdown.

#### IV. CONCLUSION:

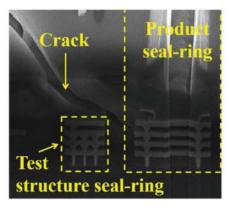

Our results indicate that probing of the test structures placed on dicing streets has a detrimental impact on narrow pad integrity as it creates cracks diving from the passivation through the BEOL layers that could even reach the product seal-ring and compromise its integrity (Figure 14). These cracks trigger an ingress of moisture after only few days of storage at room condition. This leads to significant degradation of leakage and time-to-breakdown of the low-k intermetallic dielectric. Moreover, as moisture impacts many devices such as OxRAM [3], Flash [4], DRAM [5], [6] and MOSFET [7], it is mandatory to pay heed to narrow pad probing to avoid unreliable characterizations. Furthermore, it has been reported that wire bonding can create cracks diving from the passivation through the BEOL [8]. Consequently, to avoid damaging bonding or wrong wafer quality assessment and thus compromised chips shipment to customers, we advise to proceed carefully when reducing test structure pads dimensions or bonding pads dimensions.

Figure 14: Cross-section SEM image of a product seal-ring reached by a deep crack diving from test structure pad edge (not shown here).

#### ACKNOWLEDGMENTS

The authors are grateful to the STMicroelectronics Rousset Electrical Characterization and Reliability team for providing the equipment necessary to perform this study. Production and technology support staff must be thanked for allocation of resources to manufacture the samples used in this paper.

#### REFERENCES

- O. Hinsinger *et al.*, "Demonstration of an extendable and industrial 300mm BEOL integration for the 65-nm technology node," *IEEE Int. Electron Devices Meet.*, pp. 317–329, 2004.

- [2] K. D. Lee, Q. Yuan, A. Patel, Z. T. Mai, L. H. Brown, and S. English, "Moisture impact on dielectric reliability in low-k dielectric materials," *IEEE Int. Reliab. Phys. Symp. Proc.*, vol. 2016–Septe, pp. DI11-DI14, 2016.

- [3] M. Lübben, S. Wiefels, R. Waser, and I. Valov, "Processes and Effects of Oxygen and Moisture in Resistively Switching TaOx and HfOx," *Adv. Electron. Mater.*, vol. 4, no. 1, pp. 1–11, 2018.

- [4] Z. S. Wang *et al.*, "Impact of moisture from passivation on endurance and retention of NAND flash memory," *IEEE Trans. Electron Devices*, vol. 60, no. 1, pp. 254–259, 2013.

- [5] S. Park, G. Yoon, S. Jang, and D. A. Team, "CMOSFET Characteristics Induced by Moisture Difision fi-om Inter-Layer Dielectric in 0.23um DRAM Technology with Shallow Trench Isolation," pp. 164–168, 2000.

- [6] I. G. Kim et al., "Interlayer dielectric (ILD)-related edge channel effect in high density DRAM cell," *Tech. Dig. - Int. Electron Devices Meet.*, no. Ild, pp. 827–830, 2002.

- [7] Y.-H. Lee, S. Hui, and B. Sabi, "Evaluation of moisture induced hotcarrier degradation of N- and P-MOSFETs using steam stress," *Proc. IEEE Int. Electron Devices Meet.*, pp. 523–526, 1993.

- [8] C. L. Gan, E. K. Ng, B. L. Chan, and U. Hashim, "Reliability challenges of Cu wire deployment in flash memory packaging," in *Proceedings of Technical Papers - International Microsystems, Packaging, Assembly, and Circuits Technology Conference, IMPACT*, 2012, pp. 236–239.