## Sub-10 nm plasma nanopatterning of InGaAs with nearly vertical and smooth sidewalls for advanced n-fin field effect transistors on silicon

Fares Chouchane, Bassem Salem, Guillaume Gay, Mickaël Martin, Erwine Pargon, Franck Bassani, Sandrine Arnaud, Sylvain David, Reynald Alcotte, Sébastien Labau, et al.

#### ▶ To cite this version:

Fares Chouchane, Bassem Salem, Guillaume Gay, Mickaël Martin, Erwine Pargon, et al.. Sub-10 nm plasma nanopatterning of InGaAs with nearly vertical and smooth sidewalls for advanced n-fin field effect transistors on silicon. Journal of Vacuum Science & Technology B, Nanotechnology and Microelectronics, 2017, 35 (2), 10.1116/1.4975796. hal-01891230

### HAL Id: hal-01891230 https://hal.univ-grenoble-alpes.fr/hal-01891230v1

Submitted on 28 Sep 2022

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Sub-10 nm plasma nanopatterning of InGaAs with nearly vertical and smooth sidewalls for advanced n-fin field effect transistors on silicon

Fares Chouchane, Bassem Salem, a) Guillaume Gay, Mickael Martin, Erwine Pargon, Franck Bassani, Sandrine Arnaud, Sylvain David, Reynald Alcotte, Sébastien Labau, Jérémy Moeyart, and Thierry Baron

Université de Grenoble Alpes, LTM, F-38000 Grenoble, France and CNRS, LTM, F-38000 Grenoble, France

(Received 2 September 2016; accepted 23 January 2017; published 13 February 2017)

This work focuses on the nanopatterning of sub-10 nm InGaAs fins by inductively coupled plasma reactive ion etching for advanced III-V n-fin field effect transistors (n-FinFETs) on silicon. First, different chlorine chemistries have been investigated and compared in order to select the most adequate one for the FinFETs process. Following this analysis, the BCl<sub>3</sub>/SiCl<sub>4</sub>/Ar mixture was selected for the remaining of the work. Thus, a systematic study of the etching process based on this chemistry has been carried out, and the effects of the experimental conditions on the etching kinetics and the sidewalls quality have been revealed. The optimized results depict 8 nm width fins with smooth (line edge roughness  $\approx 2 \text{ nm}$ ) and almost vertical (85° ± 1) sidewalls, opening the way for sub-10 nm width InGaAs FinFETs on silicon. © 2017 American Vacuum Society.

[http://dx.doi.org/10.1116/1.4975796]

#### I. INTRODUCTION

For several decades, the dimensional scaling of siliconbased transistors has been the main way for increasing the performance and reducing the cost of integrated circuits. However, by pushing the miniaturization of the complementary metal-oxide semiconductor to its ultimate dimensions, the power consumption became a tremendous impediment known by the scientific community as "the power-constrained scaling limit." The power consumption consisted of two parts: the static power associated with the leakage current and the dynamic power related to the switching in the transistor. Both of these two components increase drastically with the downscaling due to the rise of the short channel effects and the switching speed, respectively. The overcoming of this issue can be achieved through the introduction of innovative multigate architectures to enhance the channel electrostatic control and the integration of highmobility materials to reduce of the supply voltage. In this context, FinFETs have emerged as a cornerstone of ultimately scaled devices. By improving the electrostatic gating, this architecture allows us to improve the subthreshold slope, to overcome the short-channel effects, and to significantly reduce the leakage currents.<sup>2,3</sup> Furthermore, InGaAs is establishing itself as a very promising high-mobility n-channel material for advanced scaling nodes that permits to restrict the power consumption issue by reducing the supply voltage while maintaining the current level and so the switching speed.<sup>4–6</sup> The integration of this material on 300 mm silicon substrates opens the way for a volume manufacturability with a fully very large scale integration compatible process flow.<sup>7</sup>

The InGaAs fins patterning by inductively coupled plasma reactive ion etching (ICP-RIE) is a key step of FinFETs development as it concerns the definition of the channel, the most crucial part of the transistor. So, a particular interest must be dedicated to this step, especially in the case of deeply scaled dimensions where the slightest details are critical for achieving high electrical performance. Great efforts have been invested for enhanced profile verticality, sidewalls smoothness, surface stoichiometry and etch-induced damage mitigation.<sup>8</sup> Indeed, vertical-sidewall FinFETs have demonstrated better performance at low and moderately doped fins while extremely doped FinFETs are more performant when the fins sidewalls are tapered. 11,12 Furthermore, the sidewall roughness, 13 the modification of the surface stoichiometry during the etching, <sup>12</sup> and the ion bombardment-induced damage<sup>14</sup> greatly degrade the MOS interface, causing an important decline in the device reliability and electrical performance. These different aspects should be taken into account when carrying out advanced

Plasma etching of indium-containing III-V semiconductors has been investigated using chlorinated chemistries such as BCl<sub>3</sub>/Cl<sub>2</sub>,<sup>8,15</sup> Cl<sub>2</sub>/N<sub>2</sub>,<sup>16</sup> Cl<sub>2</sub>/H<sub>2</sub>/Ar,<sup>17</sup> Cl<sub>2</sub>/Ar,<sup>18</sup> SiCl<sub>4</sub>,<sup>19</sup> and BCl<sub>3</sub>/SiCl<sub>4</sub>/Ar. <sup>14</sup> Other gas mixtures such as CH<sub>4</sub>/H<sub>2</sub> (Ref. 20) and HBr/N2 (Ref. 21) have also been reported. However, no sub-10 nm InGaAs fins achieved by a single-step process with a vertical profile, a low surface roughness, and smooth sidewalls have been reported in the literature.

This article focuses on the characterization and development of plasma etching processes fulfilling the requirements of ultimate scaled InGaAs Fin patterning. In the first part of this work, we present the etching results of InGaAs fins with line-widths in the range of 10-50 nm using four different chlorine-based plasma chemistries in order to select the most adequate one for the fabrication of advanced III-V FinFETs. The fins' morphology has been observed by focused ion beam scanning transmission electron microscopy (FIB-STEM), and the sidewalls' roughness and the chemical composition of the surface have been analyzed, respectively, by atomic force microscopy and x-ray photoelectron spectroscopy (XPS).

a)Electronic mail: bassem.salem@cea.fr

Afterward, the effects of the different experimental conditions on the etching kinetics and the quality of the sidewalls are discussed. On completion of this study, we have demonstrated 8 nm fins with smooth and nearly vertical sidewalls. These results open the way for sub-10 nm InGaAs FinFETs on silicon.

#### II. EXPERIMENTAL SETUP

The samples used in this study are undoped  $In_{0.53}Ga_{0.47}As (25 \text{ nm})/InP (300 \text{ nm})/GaAs buffer (420 \text{ nm})$ hetero-structure, grown on a (100) orientated silicon wafer by metal organic chemical vapor deposition. The growth was performed in a 300 mm applied materials metal-organic chemical vapour deposition reactor using trimethyl-gallium and -indium as group-III precursors and tertiary butyl arsine (TBAs) and tertiary butyl phosphine (TBP) as group-V precursors.<sup>22,23</sup> Fins with line widths ranging from 10 to 50 nm and a pitch of 200 nm are defined by e-beam lithography (JOEL6300FS system) using 60 nm of hydrogen silsesquioxane (HSQ) as an etch mask. Then, samples with an area of 1  $\times$  1 cm<sup>2</sup> are bonded to a 4-in. Si carrier wafer using PMMA to avoid the use of thermal grease that could contaminate the surface. The fins patterning is performed using an Oxford Plasma Lab 100 ICP-RIE equipment with a heated chuck and backside He cooling. A systematic study was carried out to investigate the effects of the carrier wafer, the substrate temperature, the gas flow ratios, the chamber pressure, the ICP, and radiofrequency (RF) platen powers.

After patterning, the fin profiles are characterized by scanning electron microscopy (SEM) in cross-section view using a ZEISS ULTRA<sup>+</sup> microscope in order to evaluate the fins profile as well as the etching rate. For the smallest fins with a line width inferior to 20 nm, additional observations are performed by STEM across thin lamellas prepared with FIB-STEM (Helios NanoLab 450S from FEI). The images are realized under the SEM column at 30 keV, permitting a high resolution less than 1 nm.

The sidewall line edge roughness (LER) is measured by atomic force microscopy (AFM) using a homemade setup where the sample is tilted to allow the tip to scan the sidewalls. The tip of the selected AFM probe is localized at the very end of the cantilever so that it can reach the sidewall of features and has a low aspect ratio to reduce slipping issues. The images are acquired in tapping mode to reduce the sticking, and the image size is  $2 \times 2 \ \mu m^2$ .

XPS analysis of the bottom InGaAs surface is carried out immediately after the etching (few minutes) in a customized Thermo Electron Theta 300 spectrometer, using a high resolution monochromatic Al  $K_{\alpha}$  source at 1486.6 eV. The detection angle was fixed at  $23^{\circ}$  referred to the normal of the wafer.

#### **III. RESULTS AND DISCUSSION**

#### A. Impact of wafer temperature

A first study of the etching process was performed at 20 °C using BCl<sub>3</sub>/Ar plasma chemistry. The optimization of the gas flows, the chamber pressure and the ICP and RF

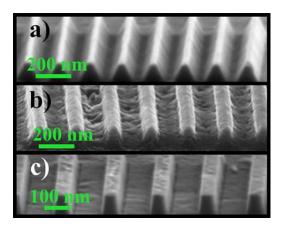

platen powers allowed obtaining fins with a smooth surface. However, for any plasma conditions investigated, the fins are tapered, and the sidewall-to substrate angle is around 60° [Fig. 1(a)].

This tapered pattern profiles at a process temperature of 20 °C is attributed to the formation of InCl<sub>x</sub> thin passivation layer at the pattern sidewalls because of the low volatility of indium chloride etch byproducts at this range of temperatures. 25 The presence of the InCl<sub>x</sub> byproducts on the InGaAs surface is confirmed by the XPS analysis shown in Fig. 2(a). The increase in the process temperature from 20 to 150 °C [Fig. 2(b)] did not solve this issue. On the contrary, at 150 °C, the GaCl<sub>x</sub> and AsCl<sub>x</sub> removal rate became much faster compared to the InClx resulting in a great increase in the surface roughness. These results are in agreement with those reported by Zhao et al., 14 for which the process temperature was varied between 100 and 250 °C. Thus, to balance the removal rate of In with respect to Ga and As, the process temperature was increased to 200 °C. At this temperature, the XPS peak associated with InCl<sub>x</sub> disappeared [Fig. 2(b)], and we observed a significant improvement in the profile slope (82°) and the sidewall smoothness [Fig. 1(c)]. We specify here that the plasma parameters had to be optimized at 200 °C in order to keep a fine control of the etching rate, which increases drastically with the temperature, and to prevent the degradation of the patterns. The best results were obtained with the following process conditions (using a silicon carrier wafer): BCl<sub>3</sub>/Ar gases ratio: 15/20 SCCM, ICP power: 50 W, RF platen power: 150 W, and chamber pressure: 3 mTorr. These conditions shall be considered as a reference point for the rest of the study.

#### B. Chlorine chemistries comparison

In order to select the most adequate chemistry, three chlorine-based mixtures are compared on the basis of the profile slope, the bottom surface roughness, surface stoichiometry, and the etching rate for a fine control of the process. Except for the chlorine gas, the other plasma parameters are kept similar to those of the reference process mentioned above. The process time is set at 20 s for all experiments. The results are summarized in Table I.

Fig. 1. (Color online) Effect of the process temperature on the sidewalls verticality: (a)  $20\,^{\circ}$ C, (b)  $150\,^{\circ}$ C, and (c)  $200\,^{\circ}$ C.

Fig. 2. (Color online) XPS spectra showing the In3d $_{5/2}$  peak of InGaAs after etching in BCl $_3$  based chemistry at (a) 20 °C and (b) 200 °C.

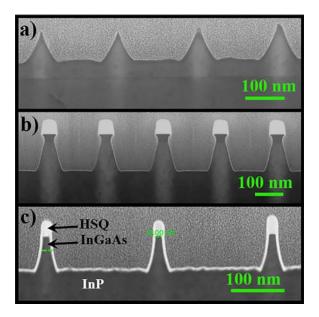

As illustrated in Fig. 3(a) and Table I, the etch rate of the Cl<sub>2</sub>-based chemistry is much higher than the other two chemistries. Moreover, the InGaAs/SiO<sub>2</sub> etch selectivity is very poor and after 20 s of plasma process, the etching mask is totally consumed, which results in degraded profiles. Indeed, by operating at 200 °C, the desorption of InCl<sub>x</sub> compounds is not anymore the limiting step, and the etching kinetics are rather driven by the supply of etching species, mainly atomic chlorine. It is suspected that in Cl<sub>2</sub> based plasma, the atomic chlorine density is higher because of the twice lower bond dissociation energies of Cl<sub>2</sub> (242.5 kJ/ mol), <sup>26</sup> compared to Si-Cl (456 kJ/mol)<sup>26</sup> and B-Cl (536 kJ/ mol).<sup>26</sup> Even after reducing the Cl<sub>2</sub> flow from 15 to 5 SCCM and the ICP power from 50 to 20 W, the etch rate of Cl<sub>2</sub>/Ar remained too high (≈11 nm/s) for a fine control of the process at 200 °C and this plasma chemistry has been abandoned.

On the other hand, the SiCl<sub>4</sub>/Ar chemistry is much less aggressive than Cl<sub>2</sub>/Ar. However, the etching rate still remains too high compared to BCl<sub>3</sub>/Ar. AFM analyses of the etched surface shows that the surface roughness (RMS) is almost similar to the one before plasma exposure for BCl<sub>3</sub>

Fig. 3. (Color online) FIB-STEM images depicting the etching profiles of 10 nm wide fins obtained with three different chlorine plasma chemistries: (a) Cl<sub>2</sub>/Ar, (b) SiCl<sub>4</sub>/Ar, and (c) BCl<sub>3</sub>/Ar.

and slightly increased for SiCl<sub>4</sub> plasma. In addition to this, a clear undercut have been observed in the case of SiCl<sub>4</sub>/Ar chemistry [Fig. 3(b)] due to its low anisotropy at low ion density. <sup>19</sup>

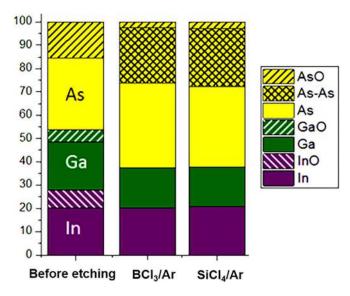

The XPS analyses of the InGaAs surface composition after exposure to  $SiCl_4/Ar$  and  $BCl_3/Ar$  plasmas (see Fig. 4 and Table I) show a great similarity between the two surfaces. Both are As rich ( $\approx 60\%$ ), which was already observed in the case of InGaAs chlorine etching 12 and could lead in some case to surface Fermi-level pining. 27 However, it is important to mention that the analyzed surface here is the postetch bottom surface. A more rigorous study requires analyzing the sidewalls composition that could be slightly different from the postetch bottom surface. This depends on the degree of the etch anisotropy as for an anisotropic etch process the bottom surface is exposed to more ion bombardment while the sidewalls could see deposition of plasma species and etch byproducts.  $^{12}$

The FIB-STEM observation and the AFM analysis of the surface show that  $BCl_3/Ar$  mixture [Fig. 3(c)] seems to be the most adequate as it provides near vertical sidewalls (82°), the lowest etch rate (2.6 nm/s) and the lowest surface roughness (RMS = 0.83 nm) among the three chemistries. To further improve the sidewall slope, a few SCCM of SiCl<sub>4</sub> were introduced to the plasma as reported by Zhao *et al.*<sup>9</sup> After optimization, the best results were obtained with 15

TABLE I. Comparison of the etching results obtained with the three chlorine-based chemistries.

| Chlorine chemistry            | Morphology                | Etching rate (nm/s) | Surface RMS (AFM 5 $\times$ 5 $\mu$ m) | Surface composition (XPS) |

|-------------------------------|---------------------------|---------------------|----------------------------------------|---------------------------|

| Before etching                | ***                       | ***                 | 0.79 nm                                | In:28% Ga:26% As:46%      |

| Cl <sub>2</sub> /Ar (15:20)   | Damaged patterns          | 15                  | ***                                    | ***                       |

| SiCl <sub>4</sub> /Ar (15:20) | Important undercut        | 7.2                 | 0.95 nm                                | In:21% Ga:18% As:61%      |

| BCl <sub>3</sub> /Ar (15:20)  | Nearly vertical sidewalls | 2.6                 | 0.83 nm                                | In:20% Ga:18% As:62%      |

Fig. 4. (Color online) XPS analysis showing the evolution of chemical composition of the InGaAs surface after exposure to BCl<sub>3</sub>/Ar and SiCl<sub>4</sub>/Ar plasmas.

SCCM of BCl<sub>3</sub>, 5 SCCM of SiCl<sub>4</sub>, and 20 SCCM of Ar [Fig. 5(a)]. For these conditions, a low etch rate of about 2.5 nm/s and a high sidewall slope of 85° are measured.

#### C. Impact of etching conditions

In the next set of experiments, the process temperature (200 °C) and the BCl<sub>3</sub>/SiCl<sub>4</sub>/Ar chemistry have been retained while the remaining RIE experimental conditions are varied and compared to the reference point described above.

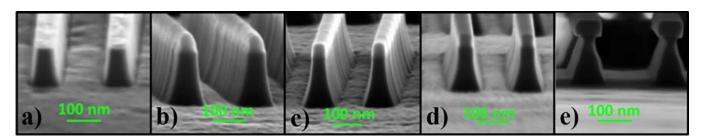

First, the impact of the carrier wafer has been studied. The SEM images [Figs. 5(a) and 5(b)] corresponding to the InGaAs fin patterning using the BCl<sub>3</sub>/SiCl<sub>4</sub> reference process with Si and SiO<sub>2</sub> carrier wafer, respectively, show similar pattern profile and sidewall angle (around  $85^{\circ} \pm 1$ ). However, the etch rate decreases sharply from 4.8 to  $2.5 \, \text{nm/s}$  with the use of a silicon wafer [Fig. 5(a)]. This is explained by the loading effect. Indeed, conversely to the inert SiO<sub>2</sub> surface, a portion of the reactive chlorine species react with the silicon surface, which represents 98.7% of the total surface and are not anymore available to etch the InGaAs sample, involving a drop of the InGaAs etching rate.

Furthermore, the increase in the Ar flow at the expense of BCl<sub>3</sub> [Fig. 5(c)] induces a rise in the etching rate of  $\approx$ 70% due to increased ion sputtering. Indeed, in the case of a high

RF platen power and a low ICP power such as our process (RF platen power: 150 W and ICP power: 50 W, bias voltage: -455 V), the physical etching due to the ion bombardment is predominant. Ar is heavier than B, Cl, and Si and its increase enhances the physical etching. On the other hand, there is no significant effect of the Ar flow increase on the sidewall slope and roughness. The effect of ICP power was also studied [Fig. 5(d)]. We have observed that when the ICP power increases from 50 to 100 W, the sidewall slope is improved and becomes quasivertical in the InGaAs part of the fins. However, the etching rate became too high (7.2 nm/s) for a fine control of the process.

The increase in the chamber pressure causes an undercut and a decrease in the etching rate. In fact, it reduces the mean path of the reactive species, and so, it promotes the ion collisions and the isotropic etching.<sup>28</sup> The decrease in the etching rate, compared to the reference sample, could be explained by a less directional ion bombardment due to the enhanced ion collisions under higher chamber pressure.<sup>29</sup>

This analysis shows that the reference conditions present a very good compromise allowing the definition fins with a high profile slope (85°), a low etching rate (2.5 nm/s), and smooth sidewalls.

# D. Sub-10 nm fins with smooth and nearly vertical sidewalls

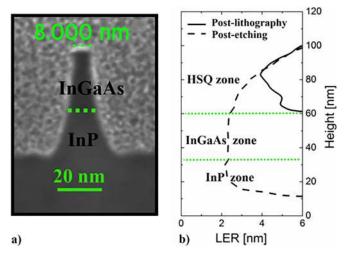

Thanks to a fine control of the e-beam lithography and the optimization of etching process, as detailed in the previous paragraph, we demonstrate 8 nm fins with quasivertical [Fig. 6(a)] and smooth sidewalls [Fig. 6(b)]. The sidewall line edge roughness (LER) has been measured using tilting AFM probe (described above in part II). This roughness is mainly due to the transfer of the HSQ mask roughness associated with the lithographic process, which is initially around 4.5 nm (the continuous line). During etching, this roughness was smoothed out to reach a value of approximately 2.5 nm at the bottom part of the HSQ mask and, respectively, 2.2 and 2 nm at the InGaAs and InP sidewalls (dashed line).

The sidewalls roughness as well as the fins width could be further reduced through a digital etch cycle based on a self-limited oxygen plasma oxidation followed by a diluted  $\rm H_2SO_4$  rinse for oxide removal, as reported in different studies.  $^{8,14,28}$

Fig. 5. (Color online) InGaAs fins obtained under different experimental conditions: (a) optimum process (ref.)  $BCl_3/SiCl_4/Ar$  flow ratio = 15/5/20 SCCM), (b) carrier wafer:  $SiO_2$  (vs Si), (c)  $BCl_3/SiCl_4/Ar$  flow ratio = 10/5/25 SCCM (vs 15/5/20 SCCM), (d) ICP power = 100 W (vs 50 W), and (e) RF platen power = 50 W (vs 150 W).

Fig. 6. (Color online) (a) FIB-STEM view of a 8 nm InGaAs fin realized using BCl<sub>3</sub>/SiCl<sub>4</sub> etch process (b) analysis by tilting AFM of the sidewall line edge roughness of the initial HSQ mask (dashed line) and the InGaAs/InP etched fins (continuous line).

#### IV. CONCLUSIONS

Sub-10 nm In<sub>0.53</sub>Ga<sub>0.47</sub>As fins integrated on silicon with a quasivertical profile (sidewall to substrate angle = 85°) and smooth sidewalls (LER  $\approx$  2 nm) have been demonstrated using BCl<sub>3</sub>/SiCl<sub>4</sub>/Ar plasma process. A systematic experimental study was carried out and allowed to reveal the impact of the different plasma parameters and identify the optimal conditions for the high resolution fins patterning. The postetch InGaAs surface was analyzed by AFM and XPS. It presents a low RMS roughness of 0.8 nm and seems to be As rich ( $\approx$ 60%). It is expected that sidewalls surface more sensitive to the chemical etching are also enriched in As. Further improvement is needed to ameliorate the surface stoichiometry. These results are very promising for the realization of advanced III–V n-FinFETs on silicon.

#### **ACKNOWLEDGMENTS**

The authors thank the members of the technical staff of the Plateforme Technologique Amont (PTA) for their technical and experimental support. This work has been partially supported by the French "Recherches Technologiques de Base" (Basis Technological Research), RENATECH programs, COMPOSE<sup>3</sup> project (FP7-ICT

#619325), and MOSINAS ANR project (ANR-13-NANO-0001).

<sup>1</sup>D. J. Frank, IBM J. Res. Dev. 46, 235 (2002).

N. Deshmukh, A. Khanzode, S. Kakde, and N. Shah, 2015 International Conference on Computer Communication and Control IC4 (2015), pp. 1–4.

Xie, X. Lin, Y. Wang, S. Chen, M. J. Dousti, and M. Pedram, IEEE Trans. Circuits Syst. 62, 761 (2015).

<sup>4</sup>J. A. del Alamo, D. A. Antoniadis, J. Lin, W. Lu, A. Vardi, and X. Zhao, 2015 IEEE Compound Semiconductor Integrated Circuit Symposium, CSICS (2015), pp. 1–4.

<sup>5</sup>Y. Q. Wu, R. S. Wang, T. Shen, J. J. Gu, and P. D. Ye, *IEDM IEEE International Electron Devices Meeting* (2009), pp. 1–4.

<sup>6</sup>Y. Hu, S. Li, G. Jiao, Y. Q. Wu, D. Huang, P. D. Ye, and M. F. Li, IEEE Trans. Nanotechnol. **12**, 806 (2013).

<sup>7</sup>N. Waldron *et al.*, IEEE Electron Device Lett. **35**, 1097 (2014).

<sup>8</sup>U. Peralagu *et al.*, ECS Trans. **69**, 15 (2015).

<sup>9</sup>X. Zhao and J. A. del Alamo, IEEE Electron Device Lett. **35**, 521 (2014).

<sup>10</sup>D. H. van Dorp, S. Arnauts, D. Cuypers, J. Rip, F. Holsteyns, S. D. Gendt, and J. J. Kelly, ECS J. Solid State Sci. Technol. 3, P179 (2014).

<sup>11</sup>A. Dixit, T. B. Hook, J. B. Johnson, E. J. Nowak, and K. V. Murali, *Physics of Semiconductor Devices*, edited by V. K. Jain and A. Verma (Springer International Publishing, Switzerland, 2014), pp. 5–8.

<sup>12</sup>T. Ivanov *et al.*, Jpn. J. Appl. Phys., Part 1 **53**, 04EC20 (2014).

<sup>13</sup>X. Tang, V. Bayot, N. Reckinger, D. Flandre, J. P. Raskin, E. Dubois, and B. Nysten, IEEE Trans. Nanotechnol. 8, 611 (2009).

<sup>14</sup>X. Zhao, J. Lin, C. Heidelberger, E. A. Fitzgerald, and J. A. del Alamo, 2013 IEEE International Electron Devices Meeting (2013), pp. 28.4.1–28.4.4.

<sup>15</sup>G. T. Edwards, D. I. Westwood, and P. M. Smowton, Semicond. Sci. Technol. 21, 513 (2006).

<sup>16</sup>S. Park, S.-S. Kim, L. Wang, and S.-T. Ho, IEEE J. Quantum Electron. 41, 351 (2005).

<sup>17</sup>J. S. Parker, E. J. Norberg, R. S. Guzzon, S. C. Nicholes, and L. A. Coldren, J. Vac. Sci. Technol., B 29, 011016 (2011).

<sup>18</sup>J. W. Bae, C. H. Jeong, J. T. Lim, H. C. Lee, G. Y. Yeom, and I. Adesida, J. Korean Phys. Soc. **50**, 1130 (2007).

<sup>19</sup>J. Etrillard, P. Ossart, G. Patriarche, M. Juhel, J. F. Bresse, and C. Daguet, J. Vac. Sci. Technol., A 15, 626 (1997).

<sup>20</sup>I. Adesida, K. Nummila, E. Andideh, J. Hughes, C. Caneau, R. Bhat, and R. Holmstrom, J. Vac. Sci. Technol., B 8, 1357 (1990).

<sup>21</sup>Y. S. Lee, M. DeVre, D. Lishan, and R. Westerman, *International Conference Indium Phosphide Related Material* (2003), pp. 78–79.

<sup>22</sup>R. Cipro et al., Appl. Phys. Lett. **104**, 262103 (2014).

<sup>23</sup>R. Alcotte et al., APL Mater. 4, 046101 (2016).

<sup>24</sup>M. Fouchier, E. Pargon, and B. Bardet, J. Appl. Phys. **113**, 104903 (2013).

<sup>25</sup>R. Chanson, S. Bouchoule, C. Cardinaud, C. Petit-Etienne, E. Cambril, A. Rhallabi, S. Guilet, and E. Blanquet, J. Vac. Sci. Technol., B 32, 011219 (2014)

<sup>26</sup>J. A. Dean, *Lange's Handbook of Chemistry* (McGraw-Hill, CA, 1992).

<sup>27</sup>T. T. Chiang and W. E. Spicer, J. Vac. Sci. Technol., A **7**, 724 (1989).

<sup>28</sup>Y. Jiao, T. de Vries, R.-S. Unger, L. Shen, H. Ambrosius, C. Radu, M. Arens, M. Smit, and J. van der Tol, J. Electrochem. Soc. **162**, E90 (2015).

<sup>29</sup>T. Maeda, J. W. Lee, R. J. Shul, J. Han, J. Hong, E. S. Lambers, S. J. Pearton, C. R. Abernathy, and W. S. Hobson, Appl. Surf. Sci. **143**, 174 (1999).